### Features

- High-performance, Low-power AVR® 8-bit Microcontroller

- RISC Architecture

- 130 Powerful Instructions Most Single Clock Cycle Execution

- 32 x 8 General Purpose Working Registers

- Fully Static Operation

- Up to 16 MIPS Throughput at 16 MHz

- On-chip 2-cycle Multiplier

- Nonvolatile Program and Data Memories

- 8K Bytes of In-System Self-programmable Flash Endurance: 10,000 Write/Erase Cycles

- Optional Boot Code Section with Independent Lock bits In-System Programming by On-chip Boot Program True Read-While-Write Operation

- 512 Bytes EEPROM

- Endurance: 100,000 Write/Erase Cycles

- 512 Bytes Internal SRAM

- Up to 64K Bytes Optional External Memory Space

- Programming Lock for Software Security

- Peripheral Features

- One 8-bit Timer/Counter with Separate Prescaler and Compare Mode

- One 16-bit Timer/Counter with Separate Prescaler, Compare Mode, and Capture Mode

- Three PWM Channels

- Programmable Serial USART

- Master/Slave SPI Serial Interface

- Programmable Watchdog Timer with Separate On-chip Oscillator

- On-chip Analog Comparator

- Special Microcontroller Features

- Power-on Reset and Programmable Brown-out Detection

- Internal Calibrated RC Oscillator

- External and Internal Interrupt Sources

- Three Sleep Modes: Idle, Power-down and Standby

- I/O and Packages

- 35 Programmable I/O Lines

- 40-pin PDIP, 44-lead TQFP, 44-lead PLCC, and 44-pad MLF

- Operating Voltages

- 2.7 5.5V for ATmega8515L

- 4.5 5.5V for ATmega8515

- Speed Grades

- 0 8 MHz for ATmega8515L

- 0 16 MHz for ATmega8515

8-bit **AVR**<sup>®</sup> Microcontroller with 8K Bytes In-System Programmable Flash

ATmega8515 ATmega8515L

# Summary

Rev. 2512ES-AVR-09/03

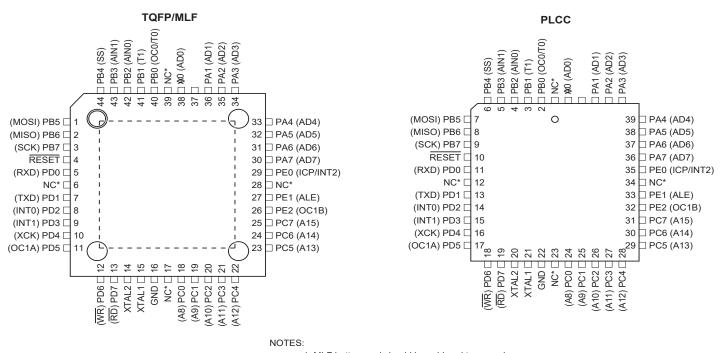

### **Pin Configurations**

#### Figure 1. Pinout ATmega8515

|                | PDIP |    |                |

|----------------|------|----|----------------|

|                |      |    | ]              |

| (OC0/T0) PB0 🗆 | 1    | 40 | □ vcc          |

| (T1) PB1 🗆     | 2    | 39 | 🗆 PA0 (AD0)    |

| (AIN0) PB2 🗆   | 3    | 38 | 🗆 PA1 (AD1)    |

| (AIN1) PB3 🗆   | 4    | 37 | 🗆 PA2 (AD2)    |

| (SS) PB4 🗆     | 5    | 36 | 🗆 PA3 (AD3)    |

| (MOSI) PB5 🗆   | 6    | 35 | 🗆 PA4 (AD4)    |

| (MISO) PB6 🗆   | 7    | 34 | 🗆 PA5 (AD5)    |

| (SCK) PB7 🗆    | 8    | 33 | 🗆 PA6 (AD6)    |

| RESET 🗆        | 9    | 32 | 🗆 PA7 (AD7)    |

| (RXD) PD0 🗆    | 10   | 31 | PE0 (ICP/INT2) |

| (TDX) PD1 🗆    | 11   | 30 | 🗆 PE1 (ALE)    |

| (INT0) PD2 🗆   | 12   | 29 | 🗆 PE2 (OC1B)   |

| (INT1) PD3 🗆   | 13   | 28 | 🗆 PC7 (A15)    |

| (XCK) PD4 🗆    | 14   | 27 | 🗆 PC6 (A14)    |

| (OC1A) PD5 🗆   | 15   | 26 | 🗆 PC5 (A13)    |

| (WR) PD6 🗆     | 16   | 25 | 🗆 PC4 (A12)    |

| (RD) PD7 🗆     | 17   | 24 | 🗆 PC3 (A11)    |

| XTAL2 🗆        | 18   | 23 | 🗆 PC2 (A10)    |

| XTAL1 🗆        | 19   | 22 | 🗆 PC1 (A9)     |

| GND 🗆          | 20   | 21 | 🗆 PC0 (A8)     |

|                |      |    | ]              |

1. MLF bottom pad should be soldered to ground.

2. \* NC = Do not connect (May be used in future devices)

### **Overview**

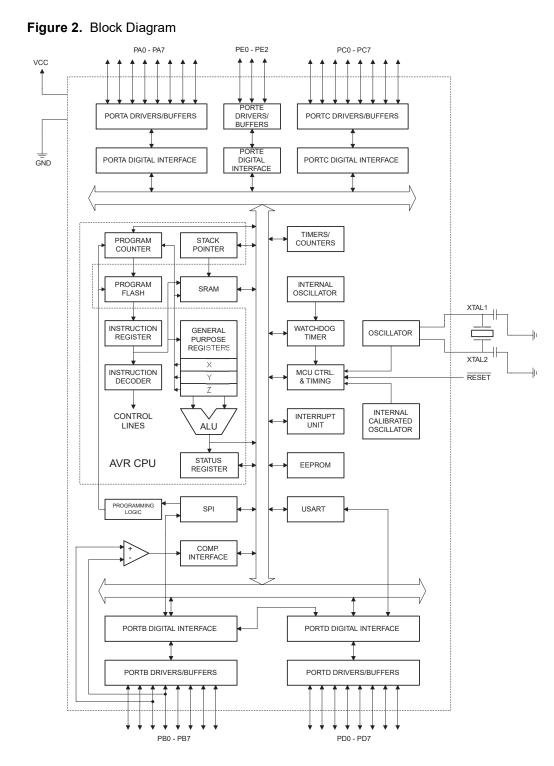

**Block Diagram**

The ATmega8515 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the ATmega8515 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

|                                                   | The AVR core combines a rich instruction set with 32 general purpose working registers.<br>All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing<br>two independent registers to be accessed in one single instruction executed in one clock<br>cycle. The resulting architecture is more code efficient while achieving throughputs up to<br>ten times faster than conventional CISC microcontrollers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                   | The ATmega8515 provides the following features: 8K bytes of In-System Programmable Flash with Read-While-Write capabilities, 512 bytes EEPROM, 512 bytes SRAM, an External memory interface, 35 general purpose I/O lines, 32 general purpose working registers, two flexible Timer/Counters with compare modes, Internal and External interrupts, a Serial Programmable USART, a programmable Watchdog Timer with internal Oscillator, a SPI serial port, and three software selectable power saving modes. The Idle mode stops the CPU while allowing the SRAM, Timer/Counters, SPI port, and Interrupt system to continue functioning. The Power-down mode saves the Register contents but freezes the Oscillator, disabling all other chip functions until the next interrupt or hardware reset. In Standby mode, the crystal/resonator Oscillator is running while the rest of the device is sleeping. This allows very fast start-up combined with low-power consumption. |

|                                                   | The device is manufactured using Atmel's high density nonvolatile memory technology.<br>The On-chip ISP Flash allows the Program memory to be reprogrammed In-System<br>through an SPI serial interface, by a conventional nonvolatile memory programmer, or<br>by an On-chip Boot program running on the AVR core. The boot program can use any<br>interface to download the application program in the Application Flash memory. Soft-<br>ware in the Boot Flash section will continue to run while the Application Flash section is<br>updated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU<br>with In-System Self-programmable Flash on a monolithic chip, the Atmel ATmega8515<br>is a powerful microcontroller that provides a highly flexible and cost effective solution to<br>many embedded control applications.                                                                                                                        |

|                                                   | The ATmega8515 is supported with a full suite of program and system development tools including: C Compilers, Macro assemblers, Program debugger/simulators, In-cir-cuit Emulators, and Evaluation kits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Disclaimer                                        | Typical values contained in this datasheet are based on simulations and characteriza-<br>tion of other AVR microcontrollers manufactured on the same process technology. Min<br>and Max values will be available after the device is characterized.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| AT90S4414/8515 and<br>ATmega8515<br>Compatibility | The ATmega8515 provides all the features of the AT90S4414/8515. In addition, several new features are added. The ATmega8515 is backward compatible with AT90S4414/8515 in most cases. However, some incompatibilities between the two microcontrollers exist. To solve this problem, an AT90S4414/8515 compatibility mode can be selected by programming the S8515C Fuse. ATmega8515 is 100% pin compatible with AT90S4414/8515, and can replace the AT90S4414/8515 on current printed circuit boards. However, the location of Fuse bits and the electrical characteristics differs between the two devices.                                                                                                                                                                                                                                                                                                                                                                   |

| AT90S4414/8515 Compatibility                      | Programming the S8515C Fuse will change the following functionality:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Mode                                              | • The timed sequence for changing the Watchdog Time-out period is disabled. See<br>"Timed Sequences for Changing the Configuration of the Watchdog Timer" on page<br>52 for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                   | <ul> <li>The double buffering of the USART Receive Registers is disabled. See "AVR<br/>USART vs. AVR UART – Compatibility" on page 135 for details.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                   | • PORTE(2:1) will be set as output, and PORTE0 will be set as input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

4 ATmega8515(L)

ATmega8515(L)

## **Pin Descriptions**

| VCC             | Digital supply voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND             | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Port A (PA7PA0) | Port A is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port A output buffers have symmetrical drive characteristics with both high sink and source capability. When pins PA0 to PA7 are used as inputs and are externally pulled low, they will source current if the internal pull-up resistors are activated. The Port A pins are tri-stated when a reset condition becomes active, even if the clock is not running. |

|                 | Port A also serves the functions of various special features of the ATmega8515 as listed on page 66.                                                                                                                                                                                                                                                                                                                                                                     |

| Port B (PB7PB0) | Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.                                |

|                 | Port B also serves the functions of various special features of the ATmega8515 as listed on page 66.                                                                                                                                                                                                                                                                                                                                                                     |

| Port C (PC7PC0) | Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port C output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active, even if the clock is not running.                                |

| Port D (PD7PD0) | Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.                                |

|                 | Port D also serves the functions of various special features of the ATmega8515 as listed on page 71.                                                                                                                                                                                                                                                                                                                                                                     |

| Port E(PE2PE0)  | Port E is an 3-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port E output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port E pins that are externally pulled low will source current if the pull-up resistors are activated. The Port E pins are tri-stated when a reset condition becomes active, even if the clock is not running.                                |

|                 | Port E also serves the functions of various special features of the ATmega8515 as listed on page 73.                                                                                                                                                                                                                                                                                                                                                                     |

| RESET           | Reset input. A low level on this pin for longer than the minimum pulse length will gener-<br>ate a reset, even if the clock is not running. The minimum pulse length is given in Table<br>18 on page 45. Shorter pulses are not guaranteed to generate a reset.                                                                                                                                                                                                          |

| XTAL1           | Input to the inverting Oscillator amplifier and input to the internal clock operating circuit.                                                                                                                                                                                                                                                                                                                                                                           |

| XTAL2           | Output from the inverting Oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                          |

以上内容仅为本文档的试下载部分,为可阅读页数的一半内容。如 要下载或阅读全文,请访问: <u>https://d.book118.com/01533434402</u> 0011300