# 第2章 开发工具的 介绍和使用

### 2.1 Vivado软件的介绍

Vivado 设计套件是Xilinx厂商于2008年研发的,2012年发布的高度集成FPGA开发环境。Vivado彻底完善了FPGA硬件开发堆栈的基础,提供系统到IC级别的设计工具,旨在提供超高生产力的设计方法。Vivado是在原有ISE设计套件的基础上研发的,在各方面性能上有很大改进,比如数据格式的统一、业界的标准性、强大的脚本功能,可以使用C语言开发或在DSP上开发,仿真速度可达ISE的3倍,使用C/C++语言可将验证速度提高100倍。随着Xilinx芯片架构的持续发展,Vivado也不断增加新应用领域,比如针对嵌入式开发人员的SDSoC,为数据中心部署开发的SDAccel,以及面向Al的工具包。目前,Vivado套件支持Xilinx高端系列产品,能够在Windows系统和Linux系统下进行大型复杂系统设计,极大丰富了FPGA的应用生态。

### 2.2 Vivado软件的使用

#### 1、工程创建:

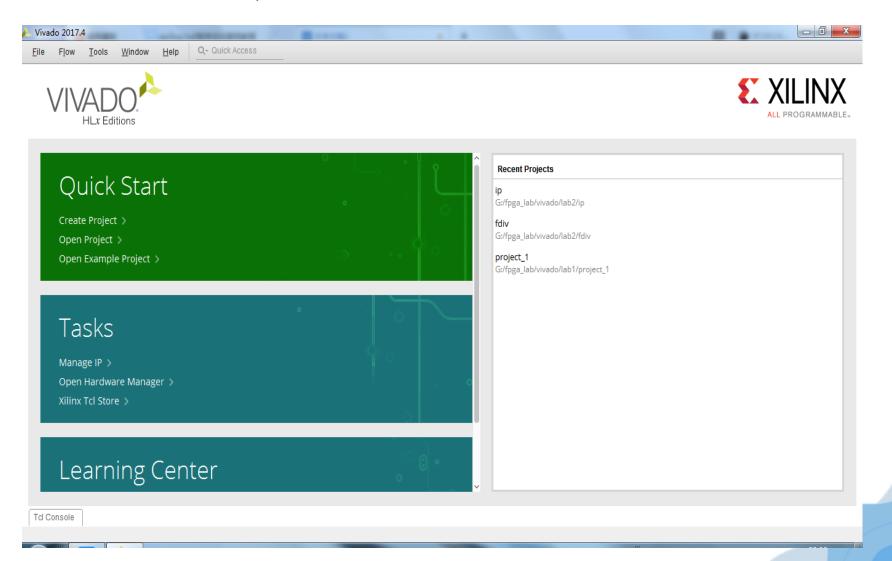

- (1) 双击Vivado软件, 弹出Vivado欢迎界面。

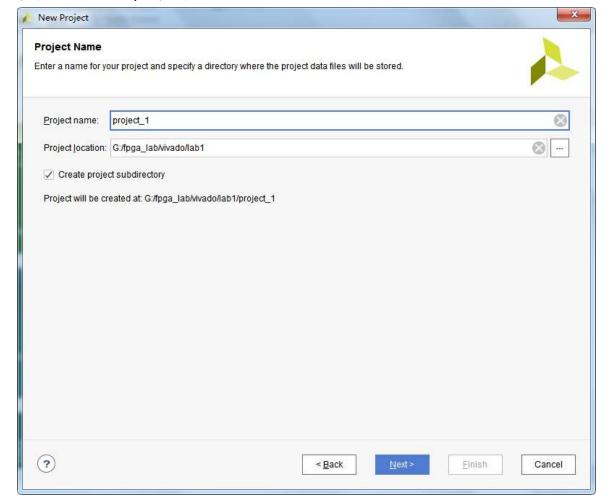

- (2) 在Quick Start中点击Creat Project选项,在New Project向导中点击Next,填写工程名和存储路径。工程名和存储路径要求必须是英文字母、数字和下划线等字符组合,并要求以英文字母开始。

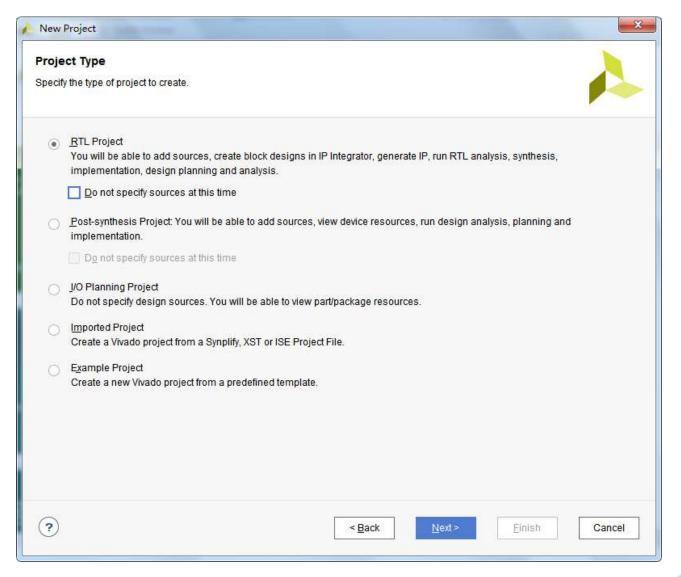

- (3) 选择RTL Project, 为工程选择类型。

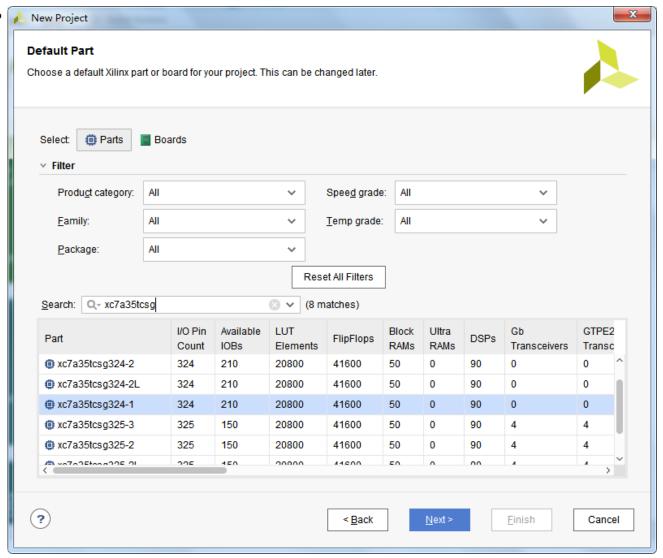

- (4) 根据自己的需要,选择一款FPGA开发芯片,在Default Part对话框中选择FPGA型号。

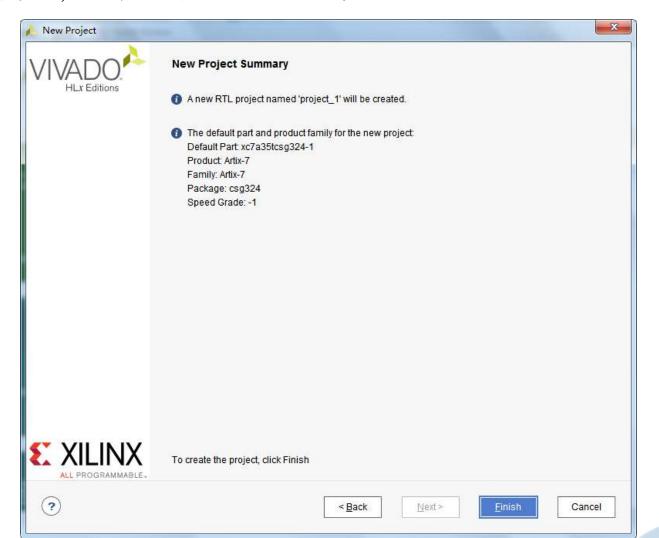

- (5) New Project Summary中显示了新建工程的硬件信息是否完整,如有异议可点击Back进行修改,无异议可点击Finish完成工程创建。

(1) 双击Vivado软件, 弹出Vivado欢迎界面。

(2) 在Quick Start中点击Creat Project选项,在New Project向导中点击Next,填写工程名和存储路径。工程名和存储路径要求必须是英文字母、数字和下划线等字符组合,并要求以英文字母开始。

(3) 选择RTL Project, 为工程选择类型。

(4) 根据自己的需要,选择一款FPGA开发芯片,在Default Part对话框中选择

FPGA型号。 New Project

(5) New Project Summary中显示了新建工程的硬件信息是否完整,如有异议可点击Back进行修改,无异议可点击Finish完成工程创建。

### 2.2 Vivado软件的使用

#### 2、添加建设文件:

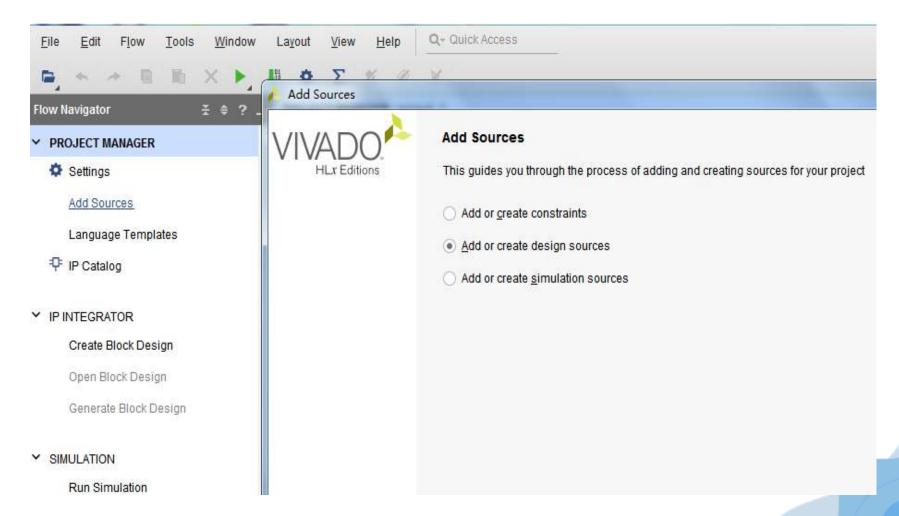

- (1) 在Vivado工程界面的PROJECT MANAGER中选择Add Sources或者在File中点击Add Sources, 选择Add or create design sources。

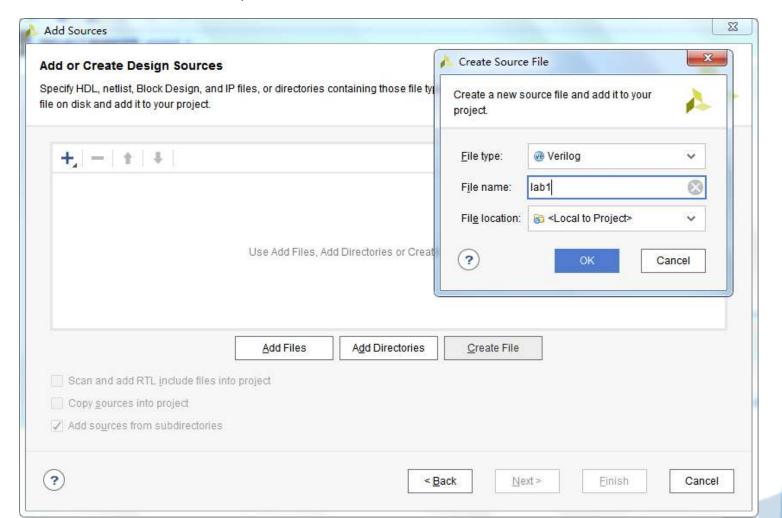

- (2) 在Add or Create Design Source向导中点击Create File,填写文件类型(lab1.v)、文件名和位置,然后点击Finish。

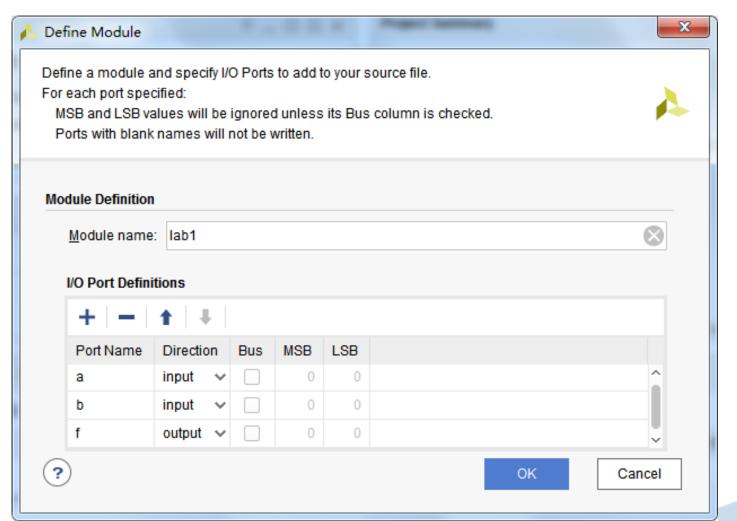

- (3) 弹出的定义模块窗口中,可以修改模块名(lab1)、定义模块端口,然后点击OK。

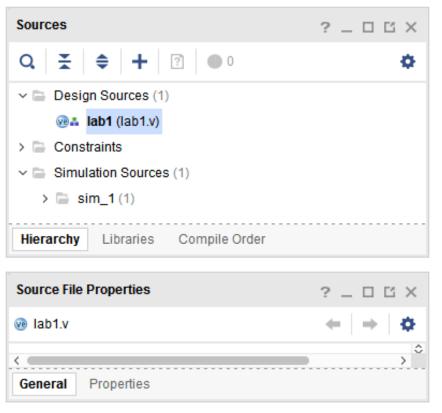

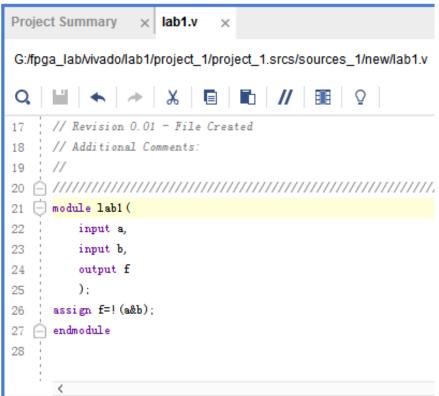

- (4) 在Sources界面中的Design Sources中双击lab1.v,在lab1.v工程文件中输入相应代码。

(1) 在Vivado工程界面的PROJECT MANAGER中选择Add Sources或者在File中点击Add Sources,选择Add or create design sources。

(2) 在Add or Create Design Source向导中点击Create File, 填写文件类型(lab1.v)、文件名和位置, 然后点击Finish。

(3) 弹出的定义模块窗口中,可以修改模块名(lab1)、定义模块端口,然后点击OK。

(4) 在Sources界面中的Design Sources中双击lab1.v,在lab1.v工程文件中输入相应代码。

### 2.2 Vivado软件的使用

#### 3、仿真:

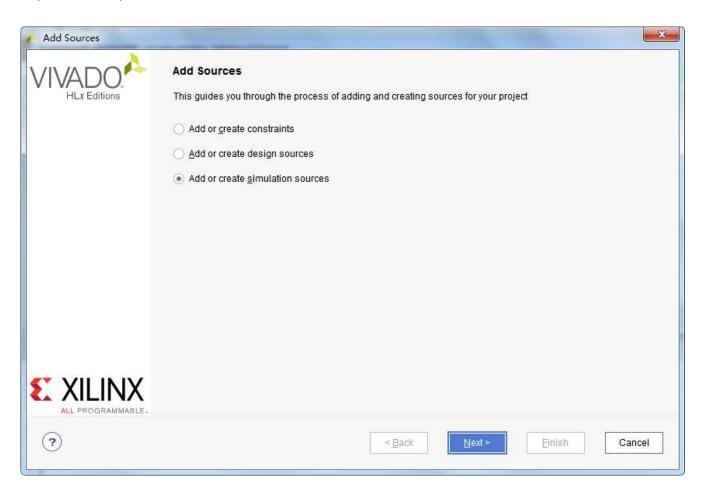

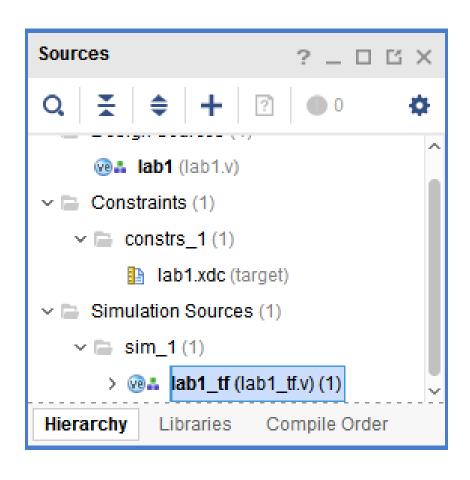

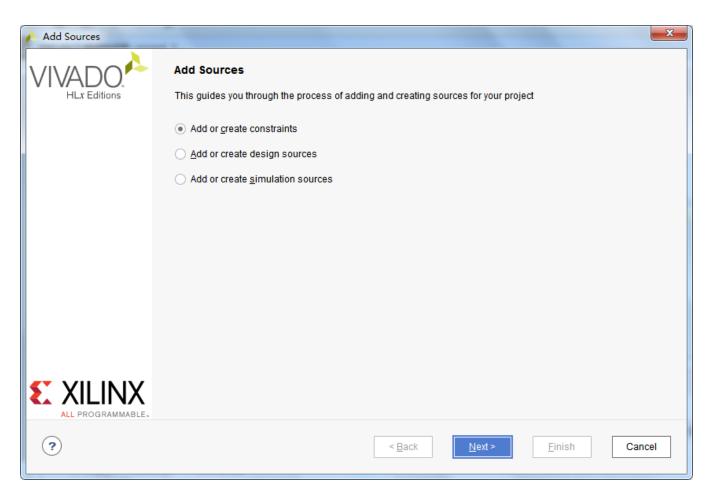

- (1) 在File中点击Add Sources, 选择Add or create simulation sources, 添加或创建仿真源文件。

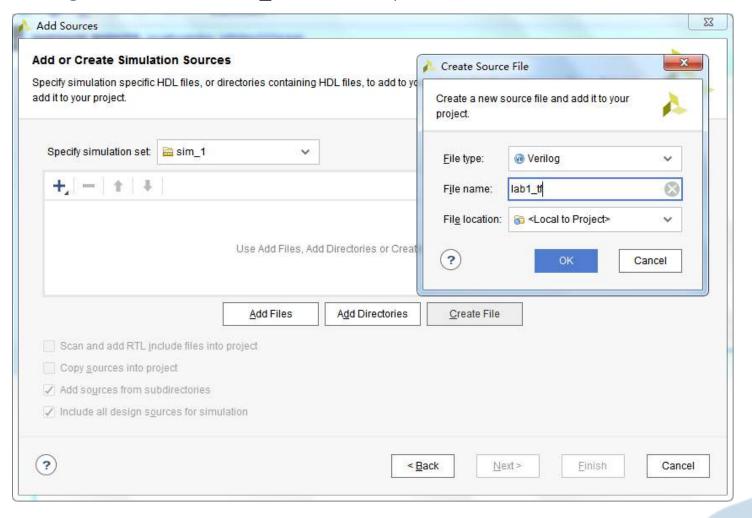

- (2) 在添加源文件向导中选择Create File, 在Create Source File中填写文件 类型(Verilog)、文件名(lab1\_tf)和位置, 然后点击Finish。

- (3) 双击Sources内Simulation Sources中的仿真文件(lab1\_tf.v)。

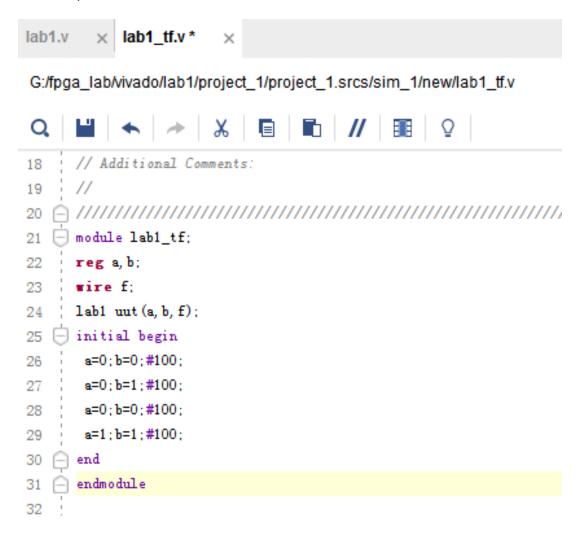

- (4) 编写测试程序。

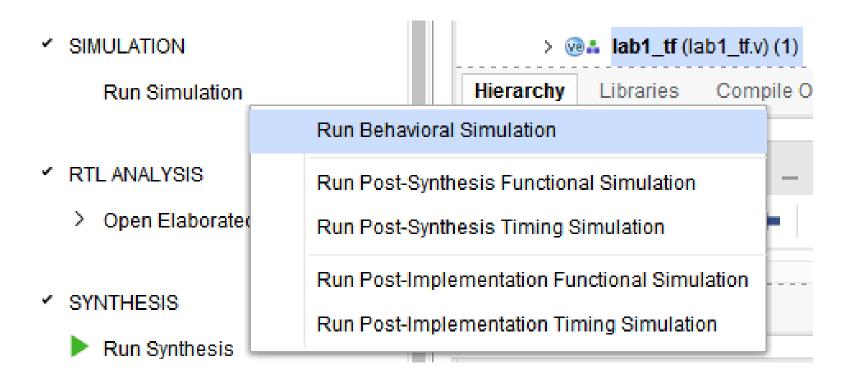

- (5) 选择SIMULATION 中的Run Simulation,运行Run Behavioral Simulation,进行行为仿真。

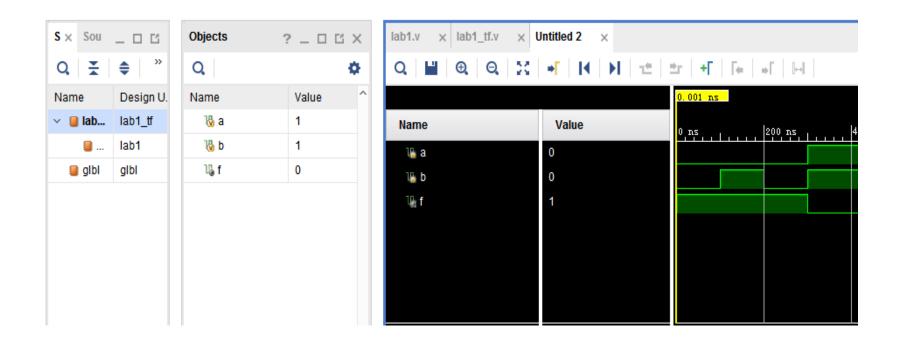

- (6) 在SIMULATION窗口中可看到相应的波形,可用Ctrl+滚轮放大或缩小仿真波形图。

(1) 在File中点击Add Sources, 选择Add or create simulation sources, 添加或创建仿真源文件。

(2) 在添加源文件向导中选择Create File, 在Create Source File中填写文件 类型(Verilog)、文件名(lab1\_tf)和位置, 然后点击Finish。

(3) 双击Sources内Simulation Sources中的仿真文件(lab1\_tf.v)。

(4) 编写测试程序。

(5) 选择SIMULATION 中的Run Simulation, 运行Run Behavioral Simulation, 进行行为仿真。

(6) 在SIMULATION窗口中可看到相应的波形,可用Ctrl+滚轮放大或缩小仿真波形图。

### 2.2 Vivado软件的使用

#### 4、约束文件:

- (1) 在File中点击Add Sources, 选择Add or create contraints, 添加或创建约束文件。

- (2) 在添加源文件向导中选择Create File, 在Create Constraints File中填写文件类型(XDC)、文件名(lab1)和位置,约束文件类型为XDC,然后点击OK和Finish。

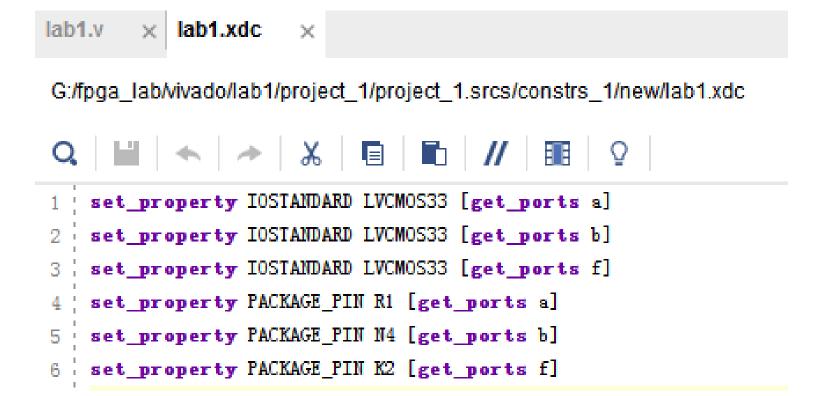

- (3) 在弹出的约束文件 lab1. xdc中,编写与开发板FPGA相对应的引脚约束条件。

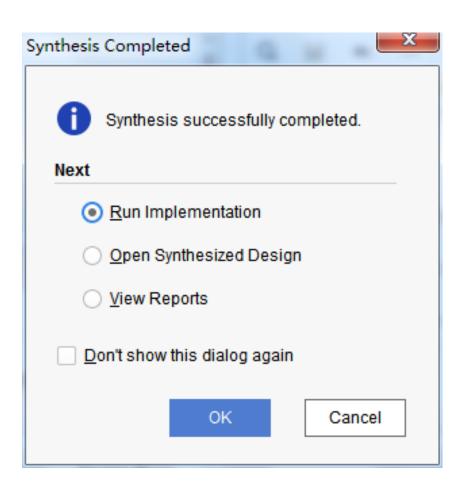

- (4) 引脚约束的另外一种方法: 在左边Flow Navigator (流动导航器) 中双击 IMPLEMENTATION中的Run Implementation (运行与实现) 进行综合和实现。

- (5) 在弹出的Synthesis Completed(完成综合)提示对话框中,选择Run Implementation后点击OK。

- (6) 在IMPLEMENTED DESIGN中的I/O Ports内,填写端口对应的引脚编号和I/O标准,并保存,这里可以将I/O Std改成LVCMOS33。

(1) 在File中点击Add Sources, 选择Add or create contraints, 添加或创建约束文件。

(2) 在添加源文件向导中选择Create File, 在Create Constraints File中填写文件类型(XDC)、文件名(lab1)和位置,约束文件类型为XDC,然后点击OK和Finish。

| ify or create constraint files for physical and timing constraint to add to your pecify constraint set: | Create Constraints File  Create a new constraints file and add it to your project |  |     |

|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--|-----|

| <b>+</b> ₄   <b>-</b>   <b>↑</b>   <b>3</b>   Use Add Files or Create File                              | Eile type:  File name:  File location:                                            |  | v ⊗ |

| Add Files Cr Cogy constraints files into project                                                        | eate File                                                                         |  |     |

(3) 在弹出的约束文件 lab1. xdc中,编写与开发板FPGA相对应的引脚约束条件。

(4) 引脚约束的另外一种方法: 在左边Flow Navigator (流动导航器) 中双击 IMPLEMENTATION中的Run Implementation (运行与实现) 进行综合和实现。

- SYNTHESIS

- Run Synthesis

- Open Synthesized Design

- ✓ IMPLEMENTATION

- Run Implementation

(5) 在弹出的Synthesis Completed(完成综合)提示对话框中,选择Run Implementation后点击OK。

以上内容仅为本文档的试下载部分,为可阅读页数的一半内容。如要下载或阅读全文,请访问: <a href="https://d.book118.com/156045042224011002">https://d.book118.com/156045042224011002</a>