# 第五章 I/O端口、输入捕捉

- · 5.1 简介

- 本章讲述dsPIC30F 系列器件I/O 端口。器件的所有引脚(除VDD、VSS、MCLR 和OSC1/CLKI 以外)均由外设和通用I/O 端口共用。通用I/O 端口可供dsPIC30F 监视和控制其他器件。大多数I/O 引脚与备用功能复用。复用将取决于不同器件上的外设功能部件。一般来说,当相应的外设使能时,其对应的引脚将不再作为通用I/O 引脚使用。

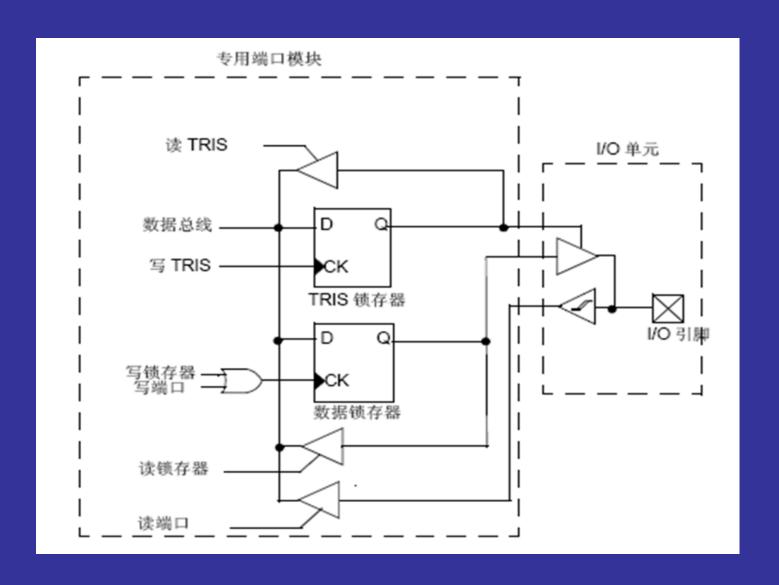

- 图5-1 所示为典型I/O 端口的框图。该框图没有画出I/O 引脚上可能复用的外设功能。

### • 图5-1: 专用端口结构框图

# 5.2 I/O 端口控制寄存器

- 所有I/O 端口都有三个与该端口的工作直接相关的寄存器, 其中字母"x"表示指定的I/O 端口号。

- TRISx: 数据方向寄存器

- PORTx: I/O 端口寄存器

- LATx: I/O 锁存寄存器

- 器件上的每个I/O 引脚在TRIS、PORT 和LAT 寄存器中都分别有一个相关的位。

- 注: 端口和可用I/O 引脚的总数将取决于不同的器件。 在一个给定的器件中,可能并没有实现端口控制寄存 器中的所有位。更多详细信息,请参阅特定的器件数 据手册。

- **5.2.1 TRIS** 寄存器

- TRISx 寄存器控制位决定与该I/O 端口相关的各个引脚是输入引脚还是输出引脚。若某个I/O 引脚的TRIS 位为"1",则该引脚是输入引脚。若某个I/O 引脚的TRIS 位为"0",则该引脚被配置为输出引脚。这很好记,因为1 很像I (input,输入), 0 很像O (output,输出)。复位以后,所有端口引脚被定义为输入。

- 5.2.2 PORT 寄存器

- 通过PORTx寄存器访问I/O引脚上的数据。读 PORTx寄存器是读取I/O引脚上的值,而写 PORTx寄存器是将值写入端口数据锁存器。

- 很多指令,如BSET 和BCLR 指令,都是读一修 改一写操作指令。因此,写一个端口就意味着读 该端口的引脚电平,修改读到的值,然后再将改 好的值写入端口数据锁存器。当与端口相关的一 些I/O 引脚被配置为输入时,在PORTx 寄存器上 使用读一修改一写命令应该特别小心。如果某个 配置为输入的I/O 引脚在过了一段时间后变成输 出引脚,则该I/O引脚上将会输出一个不期望的 值。产生这种情况的原因是读一修改一写指令读 取了输入引脚上的瞬时值,并将该值装入端口

- 数据锁存器。

- **5.2.3 LAT** 寄存器

- 与I/O 引脚相关的LATx 寄存器消除了可能在执行读一修改一写指令过程中发生的问题。读LATx寄存器将返回保存在端口输出锁存器中的值,而不是I/O 引脚上的值。对与某个I/O 端口相关的LAT 寄存器进行读一修改一写操作,避免了将输入引脚值写入端口锁存器的可能性。写LATx 寄存器与写PORTx 寄存器的结果相同。

- PORT 和LAT 寄存器之间的差异可以归纳如下: 写PORTx 寄存器就是将数据值写入该端口锁存器。 写LATx 寄存器就是将数据值写入该端口锁存器。 读PORTx 寄存器就是读取I/O 引脚上的数据值。 读LATx 寄存器就是读取保存在该端口锁存器中的数据值。

- 对某个器件无效的任何位以及与其相关的数据和控制寄存器都将被禁止。这意味着对应的LATx

- 和TRISx 寄存器以及该端口引脚将读作0

## 5.3 外设复用

- 当某个外设使能时,与其相关的引脚将被禁止作为通用I/O引脚使用。可以通过输入数据路径读该I/O引脚,但该I/O端口位的输出驱动器将被禁止。

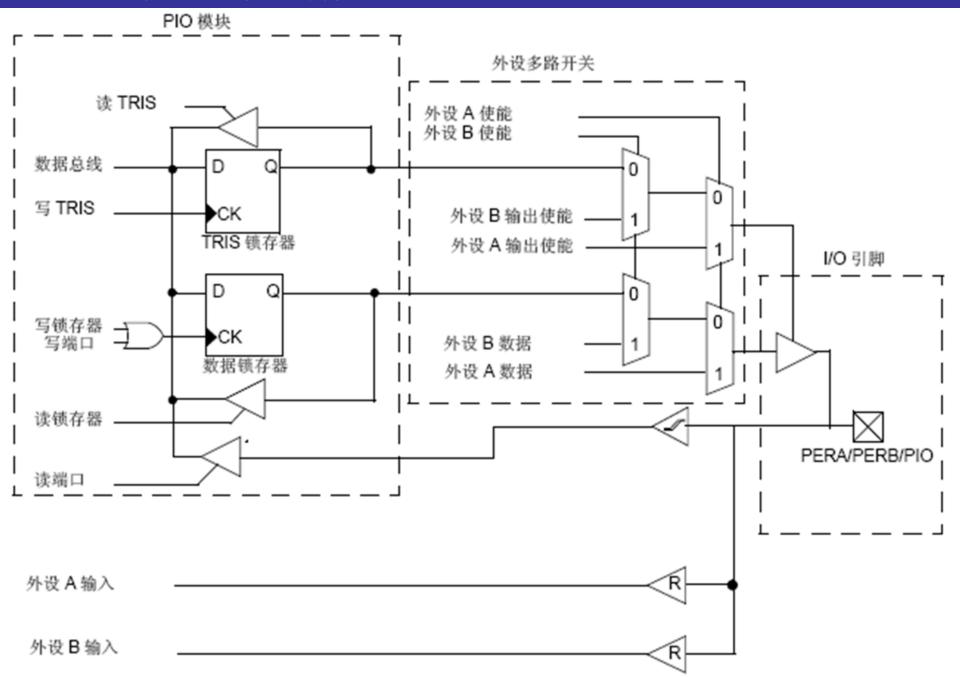

- 与另一个外设共用一个引脚的I/O 端口总是服从于该外设。外设的输出缓冲器数据和控制信号提供给一对多路开关。该多路开关选择是外设还是相关的端口拥有输出数据的所有权以及I/O 引脚的控制信号。图11-2显示了端口如何与其他外设共用,以及与外设连接的相关I/O 引脚。

- 注: 为了将PORTB 引脚用作数字I/O, ADPCFG 寄存器中的相应位必须置为"1"(即使关闭了A/D 模块也应如此)。

#### • 图5-2: 共用的端口结构框图

- 5.3.1 I/O 与多个外设复用

- 对于有些dsPIC30F 器件,尤其是那些带有少量 I/O 引脚数较少的器件,其每个I/O 引脚可能要 复用多种外设功能。图5-2 所示为两个外设与同一个I/O 引脚复用的示例。

- I/O 引脚的名称定义了与该引脚相关的各个功能 的优先级。如图11-2 所示,概念化的I/O 引脚与 两个外设复用("外设A"和"外设B"),并命名 为"PERA/PERB/PIO"。已为I/O 引脚选择了适当 的名称,以便用户可以方便地识别分配给该引脚 的功能的优先级。对于图5-2 中的示例,外设A 对引脚的控制具有最高优先权。若外设A和外设 B同时使能,外设A将控制I/O引脚。

• 5.3.1.1 软件输入引脚控制

- 分配给某个I/O 引脚的一些功能可能是那些不控 制引脚输出驱动器的输入功能。这类外设的一个 例示就是输入捕捉模块。如果使用相应的TRIS 控制位将与输入捕捉相关的I/O 引脚配置为输出 引脚,用户可以通过其相应的PORT寄存器手动 影响输入捕捉引脚的状态。这种做法在有些情形 下很有用, 尤其适用于当没有外部信号连接到输 入引脚的情况下讲行测试。

- 参照图5-2,外设多路开关的结构将决定外设输入引脚是否可以通过使用PORT寄存器用软件控制。

- 当图中所示的概念化的外设在功能被使能时,会断开 I/O 引脚与端口数据的连接。一般而言,下列外设允许 通过PORT 寄存器手动控制它们的输入引脚:

- 外部中断引脚

- 定时器时钟输入引脚

- 输入捕捉引脚

- **PWM** 故障引脚

- 大多数串行通信外设在使能时,将完全控制I/O 引脚, 所以不能通过相应的PORT 寄存器影响与该外设相关的 输入引脚。这些外设列举如下:

- SPITM

- I2CTM

- DCI

- UART

- CAN

# 5.4 端口描述

可用的I/O 端口和外设复用详情的介绍,请参阅器件数据手册。

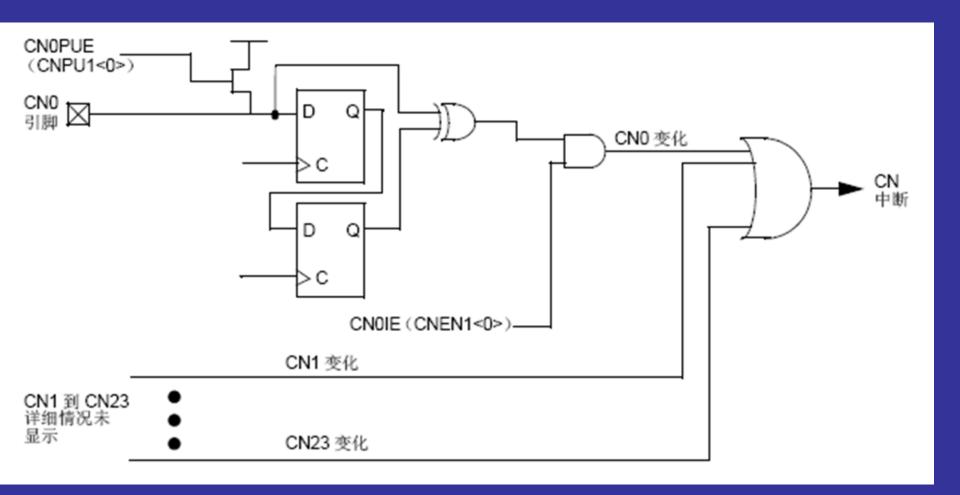

# 5.5 电平变化通知(Change Notification,CN)引脚

- 电平变化通知(CN)引脚使dsPIC30F器件能够向处理器发出中断请求,以响应所选择的输入引脚上的状态变化。可以选择(使能)多达24个输入引脚来产生CN中断。可用的CN输入引脚总数取决于所选的dsPIC30F器件。更多详细信息请参阅器件数据手册。

- · 图5-3 显示了CN 硬件的基本功能。

### • 图5-3: 输入变化通知框图

- 5.5.1 CN 控制寄存器

- 有四个与CN 模块相关的控制寄存器。CNEN1 和CNEN2 寄存器包含CNxIE 控制位,其中 "x"表示CN 输入引脚的编号。要让某个CN 输入引脚中断CPU,必须将其CNxIE 位置1。 CNPU1 和CNPU2 寄存器包含CNxPUE 控制位。

- 每个CN 引脚连接着一个弱上拉器件,该器件可以通过CNxPUE 控制位使能或禁止。弱上拉器件充当连接到该引脚的电流源,并且当连接了按钮或键盘设备时,有了该器件即可不再需要外部电阻。

- 5.5.2 CN 的配置和操作

- CN 引脚配置如下:

- 1. 通过将TRISx 寄存器中的相关位置1, 确保CN 引脚配置为数字输入引脚。

- 2. 通过将CNEN1 和CNEN2 寄存器中的相应位置1,允许所选择的CN 引脚中断。

- 3. 如果想打开所选择的CN 引脚的弱上拉器件, 请将CNPU1 和CNPU2 寄存器中的相应位

- 置1。

- 4. 清零中断标志位CNIF (IFS0<15>)。

- 5. 使用CNIP<2:0> 控制位(IPC3<14:12>) 为 CN 中断选择所需的中断优先级。

• 6. 使用CNIE (IECO<15>) 控制位允许CN 中断

- 当CN中断发生时,用户应该读与该CN引脚相关的PORT寄存器。这样做将清除引脚电平不匹配条件,并设置CN逻辑电路以检测下一次引脚电平变化。可以将当前的端口值与上一次CN中断时得到的端口读出值比较,来确定发生过变化的引脚。CN引脚有最小输入脉宽规范。

- 5.6 休眠和空闲模式下的CN 工作

- CN 模块在休眠或空闲模式下继续工作。如果使能的CN 引脚中的一个改变了状态, CNIF

- (IFS0<15>) 状态位将被置1。如果置位CNIE 位(IEC0<15>),器件将从休眠或空闲模式唤醒并恢复工作。

- · 如果为CN 中断分配的优先级等于或低于当前 CPU 的优先级,器件会从紧随SLEEP 或IDLE 指令后的那条指令继续执行。

- · 如果为CN 中断分配的优先级高于当前CPU 的优先级, 器件将从CN 中断向量地址继续执行。

• 寄存器5-1: CNEN1: 输入变化通知中断使能寄存器1

DAMD

| PV VV-U | PO VV-U | FV/VV-U | PV VV-U | FV/VV-U | / [5/ 99-9 | 0 1777-0 | P/ W-0 |

|---------|---------|---------|---------|---------|------------|----------|--------|

| CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | E CN10     | IE CN9IE | CN8IE  |

| bit 15  |         |         |         |         |            |          | bit 8  |

|         |         |         |         |         |            |          |        |

| 低字节:    |         |         |         |         |            |          |        |

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0      | R/W-0    | R/W-0  |

| CN7IE   | CN6IE   | CN5IE   | CN4IE   | CN3IE   | CN2IE      | CN1IE    | CN0IE  |

| bit 7   |         |         |         |         |            |          | bit 0  |

DAM O

$DAM_n$

DAMD

DAM O

- bit 15-0 CNxIE: 输入变化通知中断使能位

- 1= 允许输入电平变化中断

$DAM \cap$

高字节:

DMM

$D \wedge A \wedge A$

• 0= 禁止输入电平变化中断

图注:

高字节:

bit 7

DAM 0

DMM O

R= 可读位 W= 可写位 U= 未用位,读作 0

DAM O

-n= POR 时的值 1= 置位 0= 清零 x= 未知

• 寄存器5-2: CNEN2: 输入变化通知中断使能寄存器2

DAM 0

| R/W-U  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| I      |        | -      | _      | _      | _      | _      | 1      |

| bit 15 |        |        |        |        |        |        | bit 8  |

|        |        |        |        |        |        |        |        |

|        |        |        |        |        |        |        |        |

| 低字节:   |        |        |        |        |        |        |        |

| R/W-0  |

| CN23IE | CN22IE | CN21IE | CN20IE | CN19IE | CN18IE | CN17IE | CN16IE |

DAM O

DMM O

DAM O

DAMD

bit 0

- bit 15-8 未用: 读作0

- bit 7-0 CNxIE: 输入变化通知中断使能位

- 1= 允许输入电平变化中断

- 0= 禁止输入电平变化中断

### 图注:

R = 可读位 W = 可写位 U = 未用位, 读作 0 -n = 上电复位时的值 1 = 置位 0 = 清零 x = 未知

• 寄存器5-3: CNPU1: 输入变化通知上拉使能寄存器1

| 高字节:    |         |         |         |         |         |        |        |

|---------|---------|---------|---------|---------|---------|--------|--------|

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  |

| CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE | CN8PUE |

| bit 15  |         |         |         |         |         | ,      | bit 8  |

| 低子节:   |        |        |        |        |               |        |        |

|--------|--------|--------|--------|--------|---------------|--------|--------|

| R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0         | R/W-0  | R/W-0  |

| CN7PUE | CN6PUE | CN5PUE | CN4PUE | CN3PUE | CN2PUE        | CN1PUE | CN0PUE |

| bit 7  |        |        |        |        |               |        | bit 0  |

|        |        |        | _ , ,  |        | \ <del></del> |        |        |

- bit 15-0 CNxPUE: 输入变化通知上拉使能位

- 1= 使能输入电平变化上拉

- 0= 禁止输入电平变化上拉

图注:

```

R= 可读位

W= 可写位

U= 未用位,读作 0

-n= POR 时的值

1= 置位

0= 清零

x= 未知

```

• 寄存器5-4: CNPU2: 输入变化通知上拉使能寄存器2

| 高字节:   |     |     |     |     |     |     |       |

|--------|-----|-----|-----|-----|-----|-----|-------|

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 | •   |     | •   | •   | •   | •   | bit 8 |

| R/W-0   | R/W-0  |

|---------|---------|---------|---------|---------|---------|---------|--------|

| CN23PUE | CN22PUE | CN21PUE | CN20PUE | CN19PUE | CN18PUE | CN17PUE | CN16PU |

| L4 7    |         |         |         |         |         |         | Is 2   |

• bit 15-8 未用: 读作0

• bit 7-0 CNxPUE: 输入变化通知上拉使能位

- 1= 使能输入电平变化上拉

- 0= 禁止输入电平变化上拉

图注:

低字节:

R= 可读位

W= 可写位

U= 未用位, 读作 0

-n= POR 时的值

1= 置位

0= 清零 x= 未知

- 5.7 相关应用笔记

- 本节列出了与手册的本章内容相关的应用笔记。 这些应用笔记可能并不是专为dsPIC30F系列产:

• 品编写的,但是概念是相关的,通过适当修改即可使用,但在使用中可能会受到一定限制。目前与I/O 端口模块相关的应用笔记有

标题 Implementing Wake-up on Key Stroke 应用笔记编号

AN552

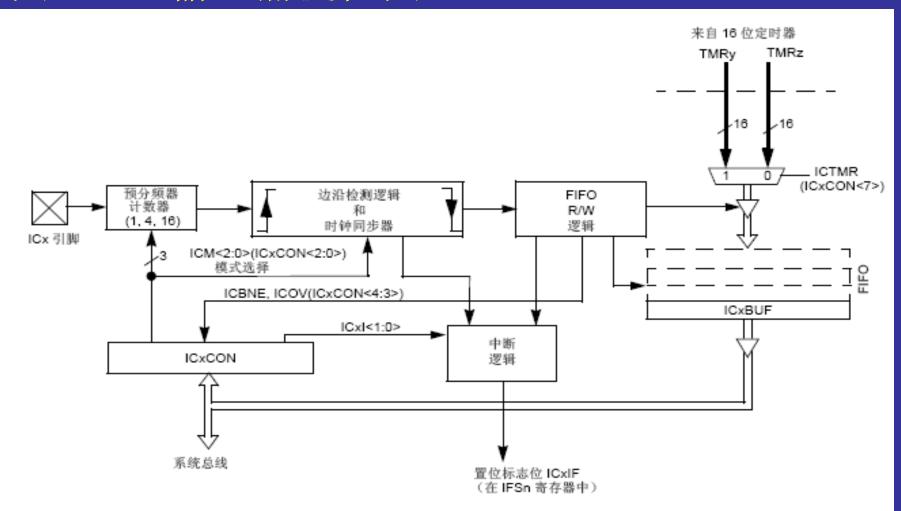

# 5-8 输入捕捉简介

• 图5-4: 输入捕捉框图

注 在信号、寄存器或位名称中的"x"表示捕捉通道的编号。

# 5.9 输入捕捉寄存器

- dsPIC30F 器件中的每个捕捉通道都有以下寄存器,寄存器名称中的"x"代表捕捉通道的编号:

- ICxCON: 输入捕捉控制寄存器

- ICxBUF: 输入捕捉缓冲寄存器

- 寄存器**5-5**: **IC**x**CON**: 输入捕捉x 控制寄存器

- 5.9.1 输入捕捉寄存器

- dsPIC30F 器件中的每个捕捉通道都有以下寄存器, 寄存器名称中的"x"代表捕捉通道的编号:

- • ICxCON: 输入捕捉控制寄存器

- • ICxBUF: 输入捕捉缓冲寄存器

- 寄存器5-5: ICxCON: 输入捕捉x 控制寄存器

| 高字节:   |     | ****   |     |     |     |     |       |

|--------|-----|--------|-----|-----|-----|-----|-------|

| U-0    | U-0 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

| _      | -   | ICSIDL | -   | -   | -   | 1   | _     |

| bit 15 | •   |        |     |     |     |     | bit 8 |

| 低字节:<br>R/W-0 | R/W-0    | R/W-0 | R-0, | НС | R-0,  | НС | R/W-0 | R/W-0    | R/W-0 |

|---------------|----------|-------|------|----|-------|----|-------|----------|-------|

| ICTMR         | ICI<1:0> |       | ICOV |    | ICBNE |    |       | ICM<2:0> |       |

| bit 7         |          |       |      |    |       |    |       |          | bit 0 |

- bit 15-14 未用: 读作0

- bit 13 ICSIDL: 输入捕捉模块在空闲时停止控制位

- 1 = 输入捕捉模块在CPU 空闲模式将停止

- 0 = 输入捕捉模块在CPU 空闲模式将继续工作

- bit 12-8 未用: 读作0

- bit 7 ICTMR: 输入捕捉定时器选择位

- 1 = 捕捉事件时捕捉TMR2 的内容

- 0 = 捕捉事件时捕捉TMR3 的内容

- 注: 可供选择的定时器可能会和上述不同。 更多详细信息请参阅器件数据手册。

- bit 6-5 ICI<1:0>: 每次中断的捕捉次数选择位

- 11 = 每4 次捕捉事件中断一次

- 10 = 每3 次捕捉事件中断一次

- 11 = 每2 次捕捉事件中断一次

- 10 = 每1 次捕捉事件中断一次

- bit 4 ICOV: 输入捕捉溢出状态标志(只读)位

- 1= 发生了输入捕捉溢出

- 0= 未发生输入捕捉溢出

- bit 3 ICBNE: 输入捕捉缓冲器空状态(只读)位

- 1 = 输入捕捉缓冲器非空,至少可以再读一次捕捉值

- 0 = 输入捕捉缓冲器为空

- bit 2-0 ICM<2:0>: 输入捕捉模式选择位

- 111 = 当器件处于休眠或空闲模式时,输入捕捉仅用做中断引脚功能

- (只检测上升沿,所有其他控制位都不适用。)

- 110 = 未使用(模块禁止)

- 101 = 捕捉模式,每16 个上升沿捕捉一次

- 100 = 捕捉模式,每4个上升沿捕捉一次

- 011 = 捕捉模式,每1个上升沿捕捉一次

- 010 = 捕捉模式,每1个下降沿捕捉一次

- 001 = 捕捉模式,每个边沿(上升沿和下降沿) 捕捉一次(ICI<1:0> 不控制该模式下的中断产生。)

- 000 = 输入捕捉模块关闭

以上内容仅为本文档的试下载部分,为可阅读页数的一半内容。如要下载或阅读全文,请访问: <a href="https://d.book118.com/488137037115006072">https://d.book118.com/488137037115006072</a>