# 微控制器体系结构基础

赵翔

xiangzh@bjtu.edu.cn

### 微控制器与PC

国家电工电子实验教学中心

大学生创新活动中心

### 微控制器与PC

# 对京交通大学 BEIJING JIAOTONG UNIVERSITY

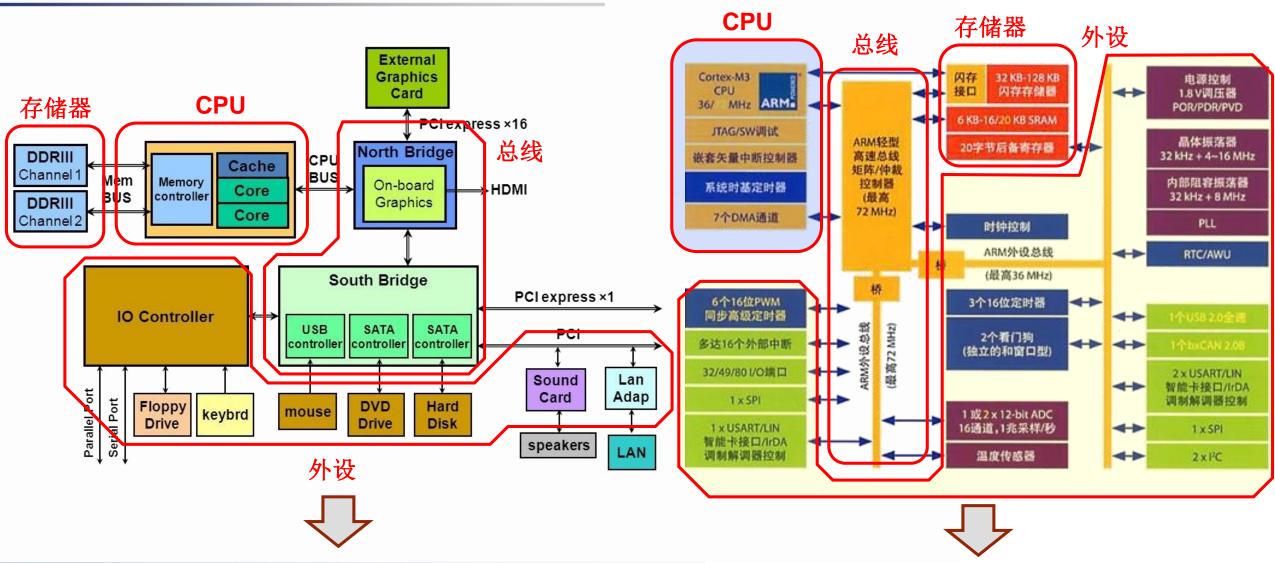

### 微控制器结构

- ▲ 处理器

- → 存储器

- → 总线

- 计算机各种功能部件之间传送信息的公共通信干线

- → 外设

- AD, Timer…

- ₩接口

≠IO、外部总线等

→ 时钟控制器 (时钟树)

大学生创新活动中心

### **+CPU**位宽

### **♣ CPU位宽**

- 按照执行指令的数据带宽定义

- 位宽同指令集、寻址空间、寄存器功能等直接相关

| 位宽     | 8位         | 16位        | 32位        |

|--------|------------|------------|------------|

| 数据总线宽度 | 8位/16位 16位 |            | 32位        |

| ALU宽度  | 8位         | 16位        | 32位        |

| 指令     | 最多8位/256种  | 最多16位      | 最多32位      |

| 寻址空间   | 理论256B     | 64kB       | 4G         |

| 常见型号   | 51、AVR     | MSP430、AVR | ARM(STM32) |

### **♯CPU**位宽

### ▲ 寻址空间

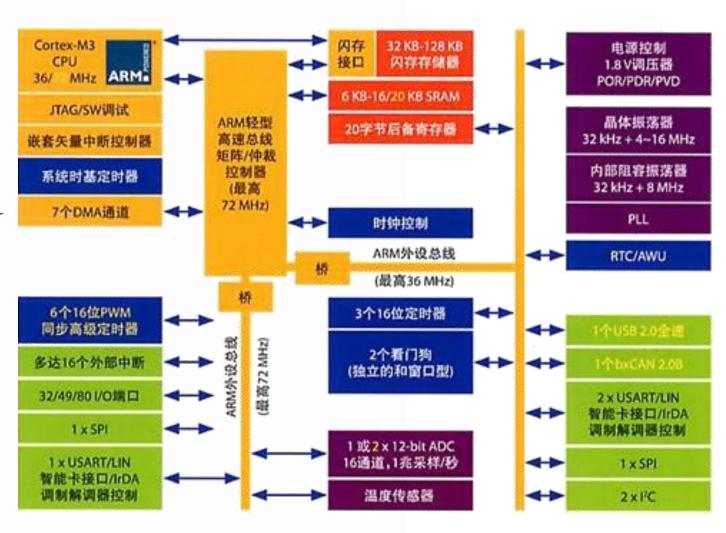

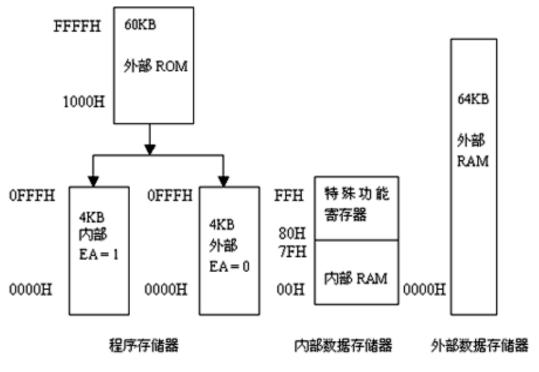

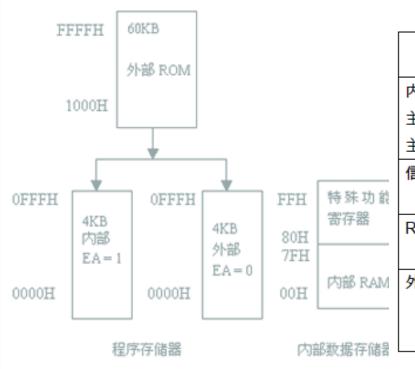

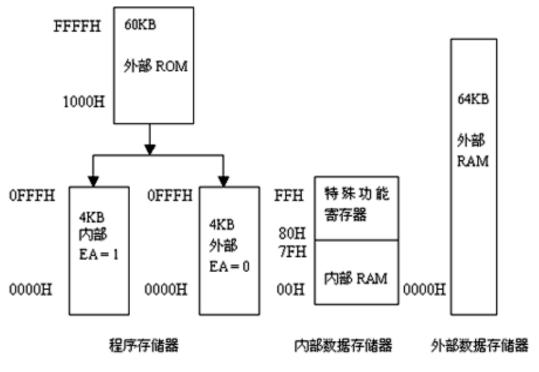

图 1 MCS-51 机的内存结构

|        |        | MSP430G2153<br>MSP430G2113 |

|--------|--------|----------------------------|

| 内存     | 尺寸     | 1kB                        |

| 主:中断矢量 | 闪存     | 0xFFFF 至 0xFFC0            |

| 主:代码内存 | 闪存     | 0xFFFF 至 0xFC00            |

| 信息内存   | 尺寸     | 256 字节                     |

|        | 闪存     | 010FFh 至 01000h            |

| RAM    | 尺寸     | 256 字节                     |

|        |        | 0x02FF 至 0x0200            |

| 外设     | 16 位   | 01FFh 至 0100h              |

|        | 8 位    | 0FFh 至 010h                |

|        | 8位 SFR | 0Fh 至 00h                  |

| 0xFFFF_FFFF                | Debug/Trace<br>Peripherals |

|----------------------------|----------------------------|

| 0xE000_0000                |                            |

| 0xDFFF_FFFF                | Unused                     |

| 0xC000_0000                |                            |

| 0xBFFF_FFFF                | Unused                     |

| 0xA000_0000                |                            |

| 0x9FFF_FFFF                | Unused                     |

| 0x8000_0000                |                            |

| 0x7FFF_FFFF                | Unused                     |

| 0x6000_0000                |                            |

| 0x5FFF_FFFF<br>0x4000_0000 | Peripherals                |

| 0x3FFF_FFFF                |                            |

| 0x2000_0000                | SRAM                       |

| 0x1FFF_FFFF                |                            |

| 0.0000 0000                | Code                       |

| 0x0000_0000                |                            |

图 6-1. Device Memory Zones

### **<b><b>↓**CPU位宽

| 0xFFFF_FFFF 0xE000_0000 | Debug/Trace<br>Peripherals |

|-------------------------|----------------------------|

| 0xDFFF_FFFF             | Unused                     |

| 0xC000_0000             |                            |

| 0xBFFF_FFFF             | Unused                     |

| 0xA000_0000             |                            |

| 0x9FFF_FFFF             | Unused                     |

| 0x8000_0000             |                            |

| 0x7FFF_FFFF             | Unused                     |

| 0x6000_0000             | Onused                     |

| 0x5FFF_FFFF             | Peripherals                |

| 0x4000_0000             |                            |

| 0x3FFF_FFFF             | SRAM                       |

| 0x2000_0000             |                            |

| 0x1FFF_FFFF             | Code                       |

| 0x0000_0000             |                            |

图 6-1. Device Memory Zones

### **<b>↓CPU**位宽

|        |        |                            | _                      |

|--------|--------|----------------------------|------------------------|

|        |        | MSP430G2153<br>MSP430G2113 | P430G2153<br>P430G2113 |

| 内存     | 尺寸     | 1kB                        | 1kB                    |

| 主:中断矢量 | 闪存     | 0xFFFF 至 0xFFC0            | FF 至 0xFFC0            |

| 主:代码内存 | 闪存     | 0xFFFF 至 0xFC00            | FF 至 0xFC00            |

| 信息内存   | 尺寸     | 256 字节                     | 256 字节                 |

|        | 闪存     | 010FFh 至 01000h            | Fh 至 01000h            |

| RAM    | 尺寸     | 256 字节                     | -256 字节<br>FF 至 0x0200 |

|        |        | 0x02FF 至 0x0200            | Fh 至 0100h             |

| 外设     | 16 位   | 01FFh 至 0100h              | Fh 至 010h              |

|        | 8 位    | 0FFh 至 010h                | Fh 至 00h               |

|        | 8位 SFR | 0Fh 至 00h                  |                        |

图 1 MCS-51 机的内存结构

| 0xFFFF_FFFF             | Debug/Trace<br>Peripherals |

|-------------------------|----------------------------|

| 0xE000_0000             |                            |

| 0xDFFF_FFFF             | Unused                     |

| 0xC000_0000             |                            |

| 0xBFFF_FFFF             | Unused                     |

| 0xA000_0000             |                            |

| 0x9FFF_FFFF             | Unused                     |

| 0x8000_0000             |                            |

| 0x7FFF_FFFF             | Unused                     |

| 0x6000_0000             |                            |

| 0x5FFF_FFFF 0x4000 0000 | Peripherals                |

| 0x3FFF FFFF             |                            |

| 0x2000_0000             | SRAM                       |

| 0x1FFF_FFFF             | Code                       |

| 0x0000_0000             |                            |

图 6-1. Device Memory Zones

### **<b>↓CPU**位宽

|      | MSP430G2153<br>MSP430G2113 |

|------|----------------------------|

| 尺寸   | 1kB                        |

| 闪存   | 0xFFFF 至 0xFFC0            |

| 闪存   | 0xFFFF 至 0xFC00            |

| 尺寸   | 256 字节                     |

| 闪存   | 010FFh 至 01000h            |

| 尺寸   | 256 字节                     |

|      | 0x02FF 至 0x0200            |

| 16 位 | 01FFh 至 0100h              |

| 8 位  | 0FFh 至 010h                |

| SFR  | 0Fh 至 00h                  |

|                         | 0                          |

|-------------------------|----------------------------|

| 0xFFFF_FFFF 0xE000 0000 | Debug/Trace<br>Peripherals |

| =                       |                            |

| 0xDFFF_FFFF             | Unused                     |

| 0xC000_0000             |                            |

| 0xBFFF_FFFF             | Unused                     |

| 0xA000_0000             |                            |

| 0x9FFF_FFFF             | Unused                     |

| 0x8000_0000             |                            |

| 0x7FFF_FFFF             | Unused                     |

| 0x6000_0000             |                            |

| 0x5FFF_FFFF             | Peripherals                |

| 0x4000_0000             |                            |

| 0x3FFF_FFFF             | SRAM                       |

| 0x2000_0000             |                            |

| 0x1FFF_FFFF             | Code                       |

| 0x0000_0000             |                            |

图 6-1. Device Memory Zones

### **♯CPU**位宽

### ▲ 寻址空间

图 1 MCS-51 机的内存结构

|        |        | MSP430G2153<br>MSP430G2113 |

|--------|--------|----------------------------|

| 内存     | 尺寸     | 1kB                        |

| 主:中断矢量 | 闪存     | 0xFFFF 至 0xFFC0            |

| 主:代码内存 | 闪存     | 0xFFFF 至 0xFC00            |

| 信息内存   | 尺寸     | 256 字节                     |

|        | 闪存     | 010FFh 至 01000h            |

| RAM    | 尺寸     | 256 字节                     |

|        |        | 0x02FF 至 0x0200            |

| 外设     | 16 位   | 01FFh 至 0100h              |

|        | 8 位    | 0FFh 至 010h                |

|        | 8位 SFR | 0Fh 至 00h                  |

| 0xFFFF_FFFF                | Debug/Trace<br>Peripherals |

|----------------------------|----------------------------|

| 0xE000_0000                |                            |

| 0xDFFF_FFFF                | Unused                     |

| 0xC000_0000                |                            |

| 0xBFFF_FFFF                | Unused                     |

| 0xA000_0000                |                            |

| 0x9FFF_FFFF                | Unused                     |

| 0x8000_0000                |                            |

| 0x7FFF_FFFF                | Unused                     |

| 0x6000_0000                |                            |

| 0x5FFF_FFFF<br>0x4000_0000 | Peripherals                |

| 0x3FFF_FFFF                |                            |

| 0x2000_0000                | SRAM                       |

| 0x1FFF_FFFF                |                            |

| 0.0000 0000                | Code                       |

| 0x0000_0000                |                            |

图 6-1. Device Memory Zones

### → 寻址空间

#### 表 5-2 TCON——定时器控制寄存器的位分配(地址 0x88、可位寻址)

| 位   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 符号  | TF1 | TR1 | TF0 | TR0 | IE1 | IT1 | IE0 | IT0 |

| 复位值 | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

#### 表 5-4 TMOD--定时器模式寄存器的位分配(地址 0x89、不可位寻址)

|  | 位  | 7    | 6    | 5      | 4         | 3    | 2     | 1    | 0    |

|--|----|------|------|--------|-----------|------|-------|------|------|

|  | 符号 | GATE | C/T  | t MI:/ | / b M0 g. | GATE | ⊕ C/T | M1   | M0   |

|  |    | (T1) | (T1) | (T1)   | (T1)      | (T0) | (T0)  | (T0) | (T0) |

#### Table 84. TIM1&TIM8 register map and reset values

| Offset | Register                                           | 31       |  | 30 | 2 8 | 0 | 17 | 56       | 25 | 24  |     | 3     | 22                  | 21         | 96    | 2 0         |                   | \$ 1   | 4              | 16        | 15                            | 14          | 13    | 12              | #      | 10               | 6         | 80             | 7              | 9     | 40        | 4     |        | m         | 2     | ,     | 0    |

|--------|----------------------------------------------------|----------|--|----|-----|---|----|----------|----|-----|-----|-------|---------------------|------------|-------|-------------|-------------------|--------|----------------|-----------|-------------------------------|-------------|-------|-----------------|--------|------------------|-----------|----------------|----------------|-------|-----------|-------|--------|-----------|-------|-------|------|

| 0x00   | TIMx_CR1                                           |          |  |    |     |   |    |          |    |     |     |       | F                   | Resi       | en    | red         |                   |        |                |           |                               |             |       |                 |        |                  |           | KD<br>:0]      | ARPE           |       | MS<br>:0] | DIR   | Mac    |           | - 1   | UDIS  | CEN  |

|        | Reset value                                        |          |  |    |     |   |    |          |    |     |     |       |                     |            | 0     | 0           | 0                 | 0      | 0              | 0         | 1                             | _           | 0     | 0               | 0      |                  |           |                |                |       |           |       |        |           |       |       |      |

| 0x04   | TIMx_CR2                                           |          |  |    |     |   |    |          |    | R   | ese | erve  | ed                  |            |       |             |                   |        |                |           | OIS3<br>OIS3<br>OIS2N<br>OIS2 |             |       |                 | OIS 1N | OIS1             | TI1S      | М              | MS<br>]        | [2:0  | 0000      | 200   | ccus   | served    | CCPC  |       |      |

|        | Reset value                                        |          |  |    |     |   |    | 0        | 0  | 0   | 0   | 0     | 0                   | 0          | 0     | 0           | 0                 | 0      | 1              | 0         | 0                             | ê.          | 0     |                 |        |                  |           |                |                |       |           |       |        |           |       |       |      |

| 0x08   | TIMx_SMCR                                          |          |  |    |     |   |    |          |    | Res | en  | ved   | i                   |            |       |             |                   |        |                |           | ETP<br>S ETF                  |             |       |                 | [3:0   | [3:0] WSW        |           |                | TS[2:0]        |       |           | SWS o |        | IS[2      | :0]   |       |      |

|        | Reset value                                        |          |  |    |     |   |    |          |    |     |     |       |                     |            |       |             |                   |        |                |           | 0                             | 0           | 0     | 0               | 0      | 0                | 0         | 0              | 0              | 0     | 0         | 0     | à      | Ž         | 0     | 0     | 0    |

| 0x0C   | TIMx_DIER                                          |          |  |    |     |   |    |          |    | R   | ese | erve  | ed                  |            |       |             |                   |        |                |           |                               | TDE         | COMDE | CC4DE           | CC3DE  | CC2DE            | CC1DE     | NDE            | BIE            | TE    | COMIE     | 004IE | TIE CO | 200       | OCZIE | OC11E | OIE  |

|        | Reset value                                        |          |  |    |     |   |    |          |    |     |     |       |                     |            | 0     | 0           | 0                 | 0      | 0              | 0         | 0                             | 0           | 0     | 0               | 0      | 1                | 0         | 0              | 0              | 0     |           |       |        |           |       |       |      |

| 0x10   | TIMx_SR                                            | Reserved |  |    |     |   |    |          |    |     |     | CC40F | CC3OF               | CC2OF      | CC10F | Reserved    | BIF               | TIF    | COMIF          | COAIF     | TISO C                        | 3           | CC2IF | CC11F           | UIF    |                  |           |                |                |       |           |       |        |           |       |       |      |

| 1      | Reset value                                        |          |  |    |     |   |    |          |    |     |     |       | 0                   | 0          | 0     | 0           | æ                 | 0      | 0              | 0         | 0                             | 1           | 0     | 0               | 0      | 0                |           |                |                |       |           |       |        |           |       |       |      |

| 0x14   | TIMx_EGR                                           | Reserved |  |    |     |   |    |          |    |     |     |       |                     |            |       |             | BG                | TG     | COMG           | 004G      |                               |             |       | 0016            | ne     |                  |           |                |                |       |           |       |        |           |       |       |      |

|        | Reset value                                        |          |  |    |     |   |    |          |    |     |     |       |                     |            |       |             |                   |        |                | _         |                               | _           |       |                 | _      |                  |           |                | 0              | 0     | 0         | 0     | _      | _         | 0     | 0     | 0    |

|        | TIMx_CCMR1<br>Output<br>Compare mode               | Rese     |  |    |     |   |    | Reserved |    |     |     | OC2CE |                     | C2<br>[2:0 |       | OC2PE       | OC2FE             | 1 :    | C2<br>S<br>:0] | OC1CE     |                               | OC1<br>[2:0 |       | 0040            | 100    | OC1FE            | 00<br>[1: | 3              |                |       |           |       |        |           |       |       |      |

| 0x18   | Reset value                                        |          |  |    |     |   |    |          |    |     |     |       |                     |            |       |             |                   |        |                |           | 0                             | 0           | 0     | 0               | 0      | ᆫ                | _         | 0              | 0              | 0     | 0         | 0     | _      |           | 0     | 0     | ш    |

|        | TIMx_CCMR1<br>Input Capture<br>mode                |          |  |    |     |   |    |          |    | Res | en  | ved   | i                   |            |       |             |                   |        |                |           | ı                             | C2F         | [3:   | 0]              | P      | 02<br>SC<br>I:0] | 1         | C2<br>S<br>:0] |                | IC1I  | F[3:      | 0]    |        | PS<br>[1: | C     | (1:   | 8    |

|        | Reset value                                        |          |  |    |     |   |    |          |    |     |     | 0     | 0                   | 0          | 0     | 0           | 0                 | 0      | 0              | 0         | 0                             | 0           | 0     | 1               |        | 0                | 0         | 0              |                |       |           |       |        |           |       |       |      |

|        | TIMx_CCMR2<br>Output<br>Compare mode               | Reserved |  |    |     |   |    |          |    | ved |     |       |                     | 024 CE     |       | )C4<br>[2:0 |                   | OC4 PE | OC4FE          |           | C4<br>S<br>:0]                | OC3CE       |       | OC3<br>[2:0     |        | OCSDE            | 3         | OC3FE          | C(<br>5<br>[1: | 6     |           |       |        |           |       |       |      |

| 0x1C   | Reset value                                        |          |  |    |     |   |    |          |    |     |     |       |                     |            |       |             |                   |        |                |           | 0                             | 0           | 0     | 0               | 0      | 0                | _         | 0              | 0              | 0     | 0         | 0     | _      |           | 0     | 0     | Щ.   |

|        | TIMx_CCMR2<br>Input Capture<br>mode<br>Reset value | Reserved |  |    |     |   |    |          |    |     |     |       | IC4F[3:0] PSC [1:0] |            |       |             | CC4<br>S<br>[1:0] |        |                | IC3F[3:0] |                               |             |       | IC<br>PS<br>[1: | С      | [1:              | 6         |                |                |       |           |       |        |           |       |       |      |

| 0x20   | TIMx_CCER                                          |          |  |    |     |   |    |          |    |     | Re  | ser   | rve                 | d          |       |             |                   |        |                |           |                               |             | CC4P  | CC4E            | CC3NP  | CC3NE            | CC3P      | CC3E           | CC2NP          | CC2NE | CC2P      | CC2E  | ON CO  | 2         | CC1NE | CC1P  | CC1E |

|        | Reset value                                        |          |  |    |     |   |    |          |    |     |     |       |                     |            | 0     | 0           | 0                 | 0      | 0              | 0         | 0                             | 0           | 0     | 0               |        | 0                | 0         | 0              | 0              |       |           |       |        |           |       |       |      |

表 5-1 的寄存器是存储定时器的计数值的。TH0/TL0 用于 T0, TH1/TL1 用于 T1。

表 5-1 定时值存储寄存器

| 名称  | 描述        | SFR 地址 | 复位值  |

|-----|-----------|--------|------|

| TH0 | 定时器 0 高字节 | 0x8C   | 0x00 |

| TL0 | 定时器0低字节   | 0x8A   | 0x00 |

| TH1 | 定时器1高字节   | 0x8D   | 0x00 |

| TL1 | 定时器1低字节   | 0x8B   | 0x00 |

表 5-2 TCON——定时器控制寄存器的位分配(地址 0x88、可位寻址)

| 位   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 符号  | TF1 | TR1 | TF0 | TR0 | IE1 | IT1 | IE0 | IT0 |

| 复位值 | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

表 5-3 TCON——定时器控制寄存器的位描述

|   |     | 7                                      |

|---|-----|----------------------------------------|

| 位 | 符号  | 描述                                     |

| 7 | TF1 | 定时器 1 溢出标志。一旦定时器 1 发生溢出时硬件置 1。清零有两种方式: |

|   |     | 软件清零,或者进入定时器中断时硬件清零。                   |

| 6 | TR1 | 定时器1运行控制位。软件置位/清零来进行启动/停止定时器。          |

| 5 | TF0 | 定时器 0 溢出标志。一旦定时器 0 发生溢出时硬件置 1。清零有两种方式: |

|   |     | 软件清零,或者进入定时器中断时硬件清零。                   |

| 4 | TR0 | 定时器 0 运行控制位。软件置位/清零来进行启动/停止定时器。        |

| 3 | IE1 |                                        |

| 2 | IT1 | 外部中断部分,与定时器无关,暂且不看。                    |

| 1 | IE0 |                                        |

| 0 | IT0 |                                        |

### CPU位宽

表 5-5 TMOD--定时器模式寄存器的位描述

| 符号    | 描述                                          |

|-------|---------------------------------------------|

| T1/T0 | 在表 5-5 中,标 T1 的表示控制定时器 1 的位,标 T0 的表示控制定时器 0 |

| 11/10 | 的位。                                         |

|       | 该位被置1时为门控位。仅当'INTx'脚为高并且'TRx'控制位被置1时使能      |

| CATE  | 定时器'x',定时器开始计时,当该位被清0时,只要'TRx'位被置1,定时       |

| GATE  | 器 x 就使能开始计时,不受到单片机引脚'INTx'外部信号的干扰,常用来测      |

|       | 量外部信号脉冲宽度。这是定时器一个额外功能,本节课暂不介绍。              |

| C/T   | 定时器或计数器选择位。该位被清零时用作定时器功能(内部系统时钟),           |

| C/1   | 被置1用作计数器功能。//blog.csdn.net/                 |

表 5-6 TMOD--定时器模式寄存器 M1/M0 工作模式

| Ml | M0 | 工作模式 | 描述                                          |

|----|----|------|---------------------------------------------|

| 0  | 0  | 0    | 兼容 8048 单片机的 13 位定时器, THn 的 8 位和 TLn 的 5 位组 |

|    | _  |      | 成一个13位定时器。                                  |

| 0  | 1  | 1    | THn 和 TLn 组成一个 16 位的定时器。                    |

| 1  | 0  | 2    | 8 位自动重装模式,定时器溢出后 THn 重装到 TLn 中。             |

| 1  | 1  | 3    | 禁用定时器 1, 定时器 0 变成 2 个 8 位定时器。               |

### **<b><b>↓**CPU位宽

## **<b>+CPU**位宽

| 2 | 高级控制     | 制定时器(TIM1 和TIM8)                        | 157 |

|---|----------|-----------------------------------------|-----|

|   | 12.1 TIM | 1和TIM8简介                                | 157 |

|   | 12.2 TIM | 1和TIM8主要特性                              | 157 |

|   | 12.3 TIM | 1和TIM8功能描述                              | 158 |

|   | 12.3.1   | 时基单元                                    | 158 |

|   | 12.3.2   | 计数器模式                                   | 160 |

|   | 12.3.3   | 重复计数器                                   | 167 |

|   | 12.3.4   | 时钟选择                                    | 168 |

|   | 12.3.5   | 捕获/比较通道                                 | 171 |

|   | 12.3.6   | 输入捕获模式                                  | 173 |

|   | 12.3.7   | PWM输入模式                                 | 174 |

|   | 12.3.8   | 强置输出模式                                  | 174 |

|   | 12.3.9   | 输出比较模式                                  | 175 |

|   | 12.3.10  | PWM模式                                   | 176 |

|   | 12.3.11  |                                         | 178 |

|   | 12.3.12  |                                         | 179 |

|   | 12.3.13  |                                         | 180 |

|   | 12.3.14  | ,                                       | 181 |

|   | 12.3.15  |                                         | 182 |

|   | 12.3.16  | 777                                     | 183 |

|   | 12.3.17  |                                         | 185 |

|   | 12.3.18  |                                         | 185 |

|   | 12.3.19  |                                         | 187 |

|   | 12.3.20  | 7 - 7 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - | 190 |

|   | 12.3.21  | 调试模式                                    | 190 |

| I2.4 TIM1₹ | 和TIM8寄存器描述              | 191 |

|------------|-------------------------|-----|

| 12.4.1     | 控制寄存器1(TIMx_CR1)        | 191 |

| 12.4.2     | 控制寄存器2(TIMx_CR2)        | 192 |

| 12.4.3     | 从模式控制寄存器(TIMx_SMCR)     | 193 |

| 12.4.4     | DMA/中断使能寄存器(TIMx_DIER)  | 195 |

| 12.4.5     | 状态寄存器(TIMx_SR)          | 196 |

| 12.4.6     | 事件产生寄存器(TIMx_EGR)       | 197 |

| 12.4.7     | 捕获/比较模式寄存器1(TIMx_CCMR1) | 198 |

| 12.4.8     | 捕获/比较模式寄存器2(TIMx_CCMR2) | 200 |

| 12.4.9     | 捕获/比较使能寄存器(TIMx_CCER)   | 202 |

| 12.4.10    | 计数器(TIMx_CNT)           | 203 |

| 12.4.11    | 预分频器(TIMx_PSC)          | 204 |

| 12.4.12    | 自动重装载寄存器(TIMx_ARR)      | 204 |

| 12.4.13    | 重复计数寄存器(TIMx_RCR)       | 204 |

| 12.4.14    | 捕获/比较寄存器1(TIMx_CCR1)    | 205 |

| 12.4.15    | 捕获/比较寄存器2(TIMx_CCR2)    | 205 |

| 12.4.16    | 捕获/比较寄存器3(TIMx_CCR3)    | 205 |

| 12.4.17    | 捕获/比较寄存器(TIMx_CCR4)     | 206 |

| 12.4.18    | 刹车和死区寄存器(TIMx_BDTR)     | 206 |

| 12.4.19    | DMA控制寄存器(TIMx_DCR)      | 208 |

| 12.4.20    | 连续模式的DMA地址(TIMx_DMAR)   | 208 |

|            |                         |     |

## 中新

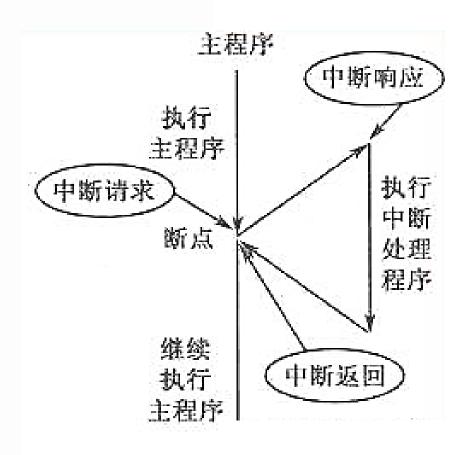

### → 中断

- 当CPU正在处理内部数据时,外界发生了紧急情况,要求CPU暂停当前的工作转去处理这个异步事件。处理完后,再回到原来被中断的地址,继续原来的工作。

- 中断发生后执行的程序称为中断服务程序。

- 申请CPU中断的请求源称为中断源。

### 中新

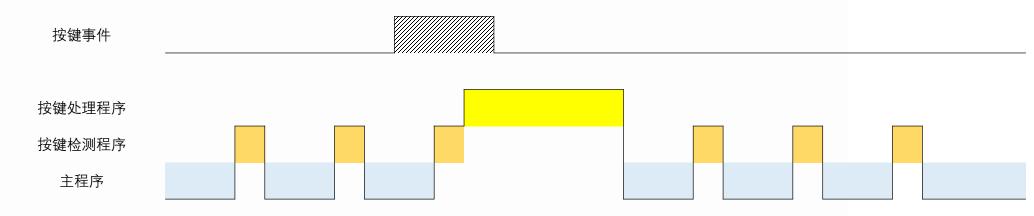

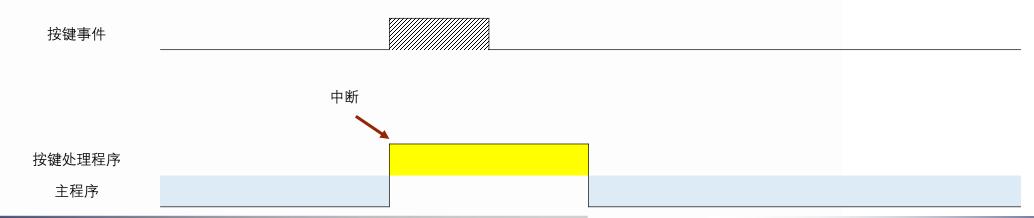

## → 不使用中断的情景-同步事件

## ▲ 使用中断的情景-异步事件

CHILDE CHILDE

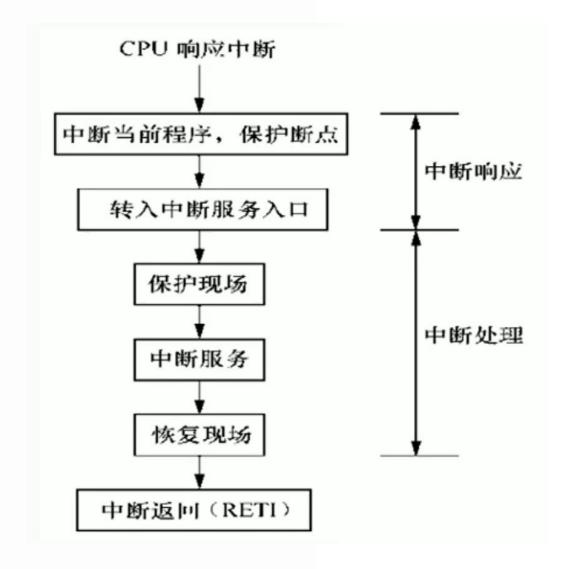

### → 中断过程

- 响应中断

- 跳转

- 保护现场

- 执行中断服务

- 恢复现场

- 中断返回

### 中断

以上内容仅为本文档的试下载部分,为可阅读页数的一半内容。如要下载或阅读全文,请访问: <a href="https://d.book118.com/55522234301">https://d.book118.com/55522234301</a> 4011302