# 基于 M6502 微处理器的验证及综合

随着系统集成技术的发展,系统级芯片 SoC(System-on-Chip) 应运而生,SoC 的出现促进了集成电路的发展。随着片上集成能力的越来越强,设计的复杂度越来越高,SoC 的设计方法和关键技术,对 IC 设计起到很大的推动作用。可重用 IP(Intellectual Property) 为 SoC 设计方法提供了一个有效的途径,可以缩短产品的设计周期,降低设计成本。本文的主要研究目标是 6502 微处理器,并对其进行验证与综合。

本文根据项目特定的功能需要对 M6502 嵌入式处理器体系结构进行设计。完成设计的过程中,将总体结构划为寄存器模块,程序计数器,取指令模块,译码模块,算术逻辑单元,回写模块和堆栈指针等单元,然后将 6502 的指令集和新的指令,以及所有的寻址方式作为设计规范要求,一起优化整个硬件系统的设计,优化之后的设计,既满足设计规范要求,又降低了设计的难度。

本文针对 M6502 微处理器验证,设计了验证平台,采用软硬件协同验证的方法对 M6502 进行验证,使用编译器在软件层次来生成测试激励,然后通过软硬件接口送入硬件验证平台,达到了高效和靶向验证 M6502 微处理器的效果。同时软硬件协同验证的方法也便于对验证结果进行判断,软件设计的测试激励可以得到验证预期,然后将硬件平台的验证结果与验证预期进行比较,可以直观有效判断验证结果的正确性。根据反馈的结果,修改软件程序,产生更为合理和有效的激励,从而全面地对其验证。最后用DesignCompiler 对设计进行了逻辑综合,设计时序和面积的约束,分析综合之后的结果,能够得到 M6502 微处理器的面积等数据。验证和综合结果表明,M6502 微处理器符合设计规范,速度可达到 20MHz,在 SMIC0.18 工艺下面积约为 1.7 万门。

关键词 微处理器:设计:验证

# VERIFICATION AND SYNTHESIS OF M6502-MICROPROCESSOR

Alongside the development of technology of system integration, SoC (System-on-Chip) has merged and promoted the development of IC (Integrated Circuit). As the capacity of integration on chip becomes stronger and the designs become more and more complex, the design method and key technology of SoC greatly promotes the design of IC. Reusable IP (Intellectual Property) provides a shortcut for SoC design, which shortens the design period of products and reduces design cost. The main study of this paper is to design an embedded microprocessor which faces intelligent battery system and is compatible with 6502 instruction set. Then the design is verified and synthesized.

In this paper, the architecture of M5602 embedded microprocessor develops that of 6502 by adding new instructions and expanding addressing mode to meet function needs specified by the project. In the process of the design, the structure is separated into register module, procedure counter, fetch module, decode module, arithmetic logic module, write back module, stack pointers and so on. Then taking 6502 instruction set, new instructions and all addressing mode as specification, the design of whole hardware system is optimized. After optimization, the design meets specification and is simplified.

In this paper, a testbench is designed for the verification of M5602 microprocessor, using software and hardware co-verification methods. By software, stimuli are generated in higher level and are sent to hardware testbench through interface between software and hardware. Such testbench can more efficiently and targeting verify M5602microprocessor. Meanwhile, they provide a comparison parameter. Verification expectation can be get from test stimulus of software and it can be compared with verification results of hardware tesetbench to

efficiently verify the correctness of verification results. Based on feed back results, software can be revised to generate more reasonable and efficient stimuli to completely verify the design. At last, by Design Compiler logic synthesis, timing constrain and size constrain are completed. By analyzing the results of synthesis, datas of M5602 microprocessor, such as area, can be gotten. From results of verification and synthesis, M5602 microprocessor meets specification, the highest frequency can reach 20MHz and by SMIC0.18 technique the area is 17 thousands gates.

Keywords microprocessor; design; verification

|   |      |                                                 | I   |

|---|------|-------------------------------------------------|-----|

|   |      |                                                 | .II |

|   |      |                                                 |     |

| 第 | 1章   | 绪论                                              | . 1 |

|   | 1.1  | 课题的背景及意义                                        | . 1 |

|   |      | 1.1.1 课题背景                                      | . 1 |

|   |      | 1.1.2 课题意义                                      | . 2 |

|   | 1.2  | 国内外研究现状                                         |     |

|   |      | 1.2.1 SoC 与 IP 技术                               |     |

|   |      | 1.2.2 8 位微处理器发展                                 |     |

|   |      | 1.2.3 6502 简介                                   |     |

|   |      | 本论文的主要内容                                        |     |

|   |      | 本论文的结构安排                                        |     |

| 第 | -    | 5 M6502 微处理器体系结构                                |     |

|   |      | M6502 体系结构                                      |     |

|   |      | M6502 指令集                                       |     |

|   |      | M6502 寻址方式                                      |     |

|   |      | M6502 微处理器存储器映                                  |     |

|   |      | 本章小结                                            |     |

| 第 |      | 5 M6502 微处理器的结构                                 |     |

|   | _    | M6502 结构                                        |     |

|   |      | 寄存器组                                            |     |

|   |      | 程序计数器                                           |     |

|   |      | 取指模块                                            |     |

|   | 3.5  | 指令译码模块                                          |     |

|   |      | 算术逻辑单元                                          |     |

|   |      | 回写模块                                            |     |

|   | 3.8  | 堆栈指示器                                           |     |

| 第 |      | 本章小结<br>5 M6502 微处理器验证与综合                       |     |

| 牙 |      | 型 M0302 减处理命验证与综合<br>验证平台设计                     |     |

|   |      | 验证                                              |     |

|   |      |                                                 |     |

|   | 4.2. | 1 测试激励生成                                        |     |

|   |      | 4.2.3 格式转换                                      |     |

|   | 12   | 4.2.3 俗                                         |     |

|   | ₹.5  | J型 MT が同才主 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | JI  |

| 4.4  | 基本功能验证                            | 33 |  |  |

|------|-----------------------------------|----|--|--|

|      | 验证结果与分析                           |    |  |  |

|      | 4.5.1 对 LDA 指令进行验证                |    |  |  |

|      | 4.5.2 对 ADC 指令(算数运算指令)进行验证        |    |  |  |

|      | 4.5.3 对 INC 指令 (加 1 减 1 指令) 进行验证  |    |  |  |

|      | 4.5.4 对 AND 指令(逻辑运算)进行验证          |    |  |  |

|      | 4.5.5 对 TAX 指令(寄存器传输)进行验证         |    |  |  |

|      | 4.5.6 对 CMP 和 BIT 指令 (比较与位检测)进行验证 | 36 |  |  |

|      | 4.5.7 对 ASL 指令(移位旋转)进行验证          | 37 |  |  |

|      | 4.5.8 对 PUSH&PULL 指令(堆栈)进行验证      | 37 |  |  |

|      | 4.5.9 对 PSR 指令进行验证                | 38 |  |  |

|      | 4.5.10 对 NOP 指令进行验证               |    |  |  |

| 4.6  | 本章小结                              | 39 |  |  |

| 结 论  |                                   | 40 |  |  |

| 致 谢  |                                   | 41 |  |  |

| 参考文献 |                                   |    |  |  |

| 附录   | 附录                                |    |  |  |

|      |                                   |    |  |  |

# 第1章 绪论

## 1.1 课题的背景及意义

了解课题的背景会让我们了解课题的本源,了解课题意义会让我们知道研究本课题的价值所在。本章将对研究课题 M6502 微处理器验证及综合的背景意义进行介绍。

#### 1.1.1 课题背景

21 世纪人类进入了信息时代,信息技术飞速发展。微处理器被广泛应用于国防、民用等各个方面,微处理器设计相关技术的发展,可以促进国内信息技术的发展,巩固国防安全。多年来,国内研究人员一直在努力开发拥有自己独立知识产权的微处理器。

目前,这个努力有了初步的成果,我国已经有一批拥有独立知识产权的 CPU,但与世界先进水平相比仍然相差较大。

嵌入式微处理器是针对特定目标应用系统而开发的微处理器,在满足功能需求的前提下,进行了特定的结构或微结构方面的优化,与通用式微处理器相比,具有成本以及面积等方面的优势。

嵌入式应用的性能和成本范围十分广泛,从简单的、只支持固化应用程序的 8 位微控制器,到具有强大的图形图像和流媒体处理能力的 32/64 位微处理器或数字信号处理器。

选择嵌入式微处理器有很多标准,其中,成本和性能是两个主要考虑方面。市场的需要迫使嵌入式微处理器设计者最大限度的去减少成本和产品面市时间,并同时提高处理器的性能和集成度[12]。

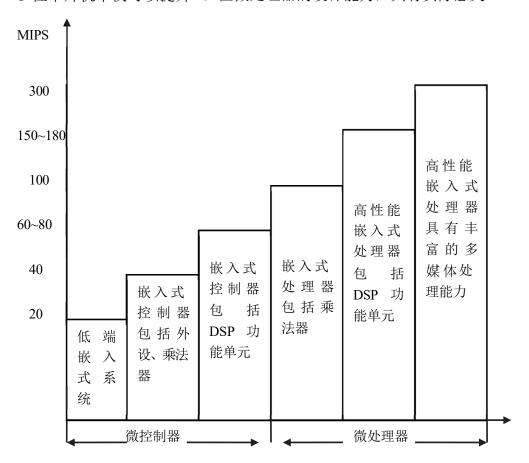

在嵌入式处理器领域,没有一种处理器可以应用于所有领域,可供选择的处理器种类很多,其中主要包括 ARM 系列 CPU、MIPS 系列 CPU、Motorola 的 68K 系列及 Hitachi 的 SuperH 等。图 1-1 概括了嵌入式处理器的发展过程。在嵌入式系统领域,8 位和 16 位处理器一直占有垄断地位。

由于 8/16 位的嵌入式处理器结果简单,所以常常并不被称为处理器,而是被称为微控制器。随着嵌入式应用对系统性能要求越来越高,嵌入式系统业越来越复杂,嵌入式微处理器的性能也与日俱增。

许多嵌入式处理器结构从过去的主要用于桌面系统的结果(如 MIP、SSPARC等)中衍生出来,与桌面处理器之间的不同也不再仅仅局限于寄存器组织、基本指令集、流水线结果,而扩展到了诸如功耗、成本、外设集成度、中断响应时间、片上 RAM 或 ROM 的容量等诸多问题[54]。

#### 1.1.2 课题意义

我国在微处理器方面的设计远远落后于发达国家,国产微处理器品种 很少,市场占有率很低。

国内从事微处理器开发的相关企业大部分都是采用进口的芯片,一方面,这是由于业界都已经习惯于以其的产品不原意采用新的芯片,另一方面,国产微处理器的性能无法满足客户的需求且大部分国产单片机为逆向设计所得没有自主知识产权。

综合考虑国内市场行情和 CISC 结构的特点,开发出一款高性价比的 8 位单片机不仅可以提升 8 位微处理器的设计能力,具有实际意义<sup>[5]</sup>。

图 1-1 嵌入式微处理器的发展

同时,知识产权核(Intellectual Property, IP)在开发和应用上都具有其独到的优势。例如,开发工作量相对较少。开发成本低,灵活性大,并容易进行工艺移植,且性能可以不断提高等等,基于以上因素,确定本论文的目标:开发兼容 6502 嵌入式微处理器 IP[67]。

#### 1.2 国内外研究现状

了解国内外的形式和发展现状对我们研究方案的制定和策略有着深远的影响。本节将对国内外的形式和发展现状进行介绍。

#### 1.2.1 SoC 与 IP 技术

随着超大规模集成电路技术的发展,SoC 和 IP 技术越来越成为 IC 业界广泛关注的焦点。基于 IP 的 SoC 技术以其易于增加新功能和上市时间短的优势,成为当前以及今后一段时间内主要的 IC 设计方法。SoC 技术是指将系统的多种功能模块集成到单一的半导体芯片上的技术。这些功能模块,诸如 CPU、DSP、用户定义的逻辑单元(UDL)等,都曾是具有完整功能的 IC 产品,现在这些模块以"核"(core)的形式嵌入 SoC 之中,他们就是所谓的 IP<sup>[8]</sup>。

SoC 将电路系统设计的可靠性、低功耗等都解决在 IC 设计之中,把过去许多需要系统设计解决的问题集中在 IC 设计中解决。系统设计工程师可以集中精力研究对象领域中的问题。SoC 是现代电子系统设计的重要选择。

IP 作为实现 SoC 设计的主要途径和核心技术,已经成为 ASIC 设计方法学中的科学分支。1997 年,CICC(Custom IC conference,转用 IC 国际年会)的"单元建库"论文分册首次出现有关 IP 的报道,而第二年 CCIC年会的 IP 论文数量已经发展到三个分册。同年,"半导体战略论坛'98"(SiliconStratergies'98)则组织了 IP 专题国际研讨会。到 1999 年更进一步发展到"ASIC Status'99"的论文总量的三分之一都是讨论 IP 的文章。最著名的微电子国际年会"半导体战略论坛"(Silicon Strategies)于 1998 年3月16日至17日在美国加州的硅谷(San Jose)召开,并把 IP 产业的现状和发展作为大会专题。共有48个全球最著名的微电子公司的主要负责人作了大会发言,声势之盛堪称史无前例。这些都展示了 IP 产业迅猛的发展势头。

IP产业的形成和发展,对我国 IC设计业来说,是个很大的机遇。IP库的建立,把"系统集成"与"功能模块设计"分开,降低了设计的难度和规模,是个适合我国设计水平的切入点。目前,SoC 已经成为微电子重大专项列入国家技术的发展(863)技术之中。而 IP是 SoC设计的基础,因此,建立和发展 IP技术及相关技术的研究,建立运作规范的 IP市场的工作非常紧迫[[0,1]]。

IP 根据不同的应用分为:微处理器核、存储器(MEMORY)核、数字/模拟混合信号电路、射频(RF)模块、I/O 接口电路、各种专用算法模块和职能电源模块等。其中,微处理器核设计复杂,同时又是 SoC 的关键部件,具有很高的研究价值。在系统级芯片中,大多都会用到微处理器核,因此微处理器 IP 需要具有良好的复用性。

#### 1.2.28 位微处理器发展

随着超大规模集成电路制造技术的飞速发展,微处理器正朝着两个明显的方向发展:一是性能不断提高,以满足高速度大容量的数据处理的通用微处理器;二是功能日趋完善,以满足诸多领域各种错综复杂的现场控制要求的嵌入式微处理器。作为计算机技术的一个重要的分支,嵌入式微处理器技术正以惊人的速度向前发展[12,13]。

自 1974 年美国仙童公司研制出世界上第一台单片微型计算机 F8 以来,单片机以及嵌入式微处理器得到了蓬勃的发展,尤其是近年来性能提高得更快。其原因除了在工艺方面的迅速微细化外,嵌入式微处理器体系结构的不断变革也起到了极其重要的作用。从结构上看,主要是依靠复杂指令计算机结构(CISC)技术来提高微处理器的性能[14,15]。到了 80 年代,在美国兴起了精简指令计算机结构(RISC)技术,它通过实现较少的指令有效地的简化了嵌入式微处理器的结构,减小了芯片的面积及功耗,促进了微处理器的性能提高。近些年来,超标量、超流水线等新结构的出现,加速了嵌入式微处理器的发展[16,17]。

80 年代以来,嵌入式微处理器市场上涌现出一大批采用 RISC 结构的 微处理器,对传统的 8051、6502 等系列单片机产生了巨大的冲击,但是采用 CISC 结构的 8051、6502 等单片机依然存在优势,这是由于 CISC 处理器具有丰富的指令系统以及多种复杂的寻址方式,指令长度灵活可变,具有处理高级语言的能力,以上几方面特点使其在嵌入式领域中仍然占据重要地位。目前属于 CISC 结构的单片机有 Intel8051、Motorola 的 M68HC 系列、Atmel 的 AT89 系列、台湾 Winbond 的 W78 系列等。

#### 1.2.3 6502 简介

6502 微处理器是一种广泛应用的大规模集成电路芯片,它同已经为我国普遍了解的 INTEL80xx 系列、ZILOG Z80 和 MOTOROLA68 系列一样,都是功能良好的 8 位微处理器。以 6502x 微处理器为基础的单片机在美国也富有声誉。其中 AIM-65 和 SYM-1 单片机在美国被认为是性价比最高的一类单片机,在美国应用相当普遍。6502 微处理器也被广泛应用于工业 控制、仪表、空间技术等许多方面。

生产 6502 的厂家主要有 RockWell、MOS Technology 和 Synertek 等公司。从硬件接线上说,它们与 MOTOROLA68 系列芯片相兼容。从体系结构上说,6502 与 MOTOROLA68 系列也是相同的,而不同于 80/Z80。

第一个队工业有重要影响的 8 位微处理器是 Ietel 公司的 8008。1973年又推出了 8080,进一步开阔了 8 位微处理器的应用市场,而后 Motorola和 Zilog 公司分别于 1974 年和 1976 年推出了 M6800 和 Z80 两种 8位微处理器。Z80 完全是与 8080 高档兼容的产品; 而 M6800 则从体系上

做了变动。这三种系列都成为 8 位微处理器中的最重要系列之一。

1975 年推出的 6502 实在 M6800 的基础上结合了工艺上的改进而产生的。从它的设计思想看,使基本功能变得更灵活,同时芯片的成本和功耗也明显降低,即重点是提高芯片的性能价格比。这使它和上述三大系列一样,挤入了 8 位微处理器市场,成为世界上销售最多的微处理器之一。

#### 1.3 本论文的主要内容

本课题的目标是对 M6502 微处理器进行验证,本论文的主要内容如下:了解 M6502 微处理器的结构,及其 构造。

之后, 搭建自动化验证平台对所做设计进行验证, 确定其功能设计是否满足功能要求。

#### 1.4 本论文的结构安排

本论文的具体结构安排如下:

第 1 章为绪论,主要介绍了论文的研究背景及意义、国内外在嵌入式 微处理器设计方面的研究现状以及本论文研究内容。

第 2 章介绍了 M6502 处理器的体系结构,从 M6502 系统结构、指令集、寻址方式以及存储器映射四个方面进行了阐述。

第 3 章详细地介绍了 M6502 微处理器各个功能模块的 结构,包括寄存器组、程计数器、取指令模块、指令译码模块、算术逻辑单元、回写模块、堆栈指示器。

第 4 章介绍了对 M6502 微处理器验证,采用软硬件协同验证的方法 队 M6502 进行了验证。

在结论部分,对全文作出总结。

# 第 2 章 M6502 微处理器体系结构

通过对功能需求的分析,确定了 M6502 微处理器的体系结构。以下分别从系统结构,指令集,寻址方式,存储器影射等几个方面对 M6502 的体系结构进行了阐述。

#### 2.1 M6502 体系结构

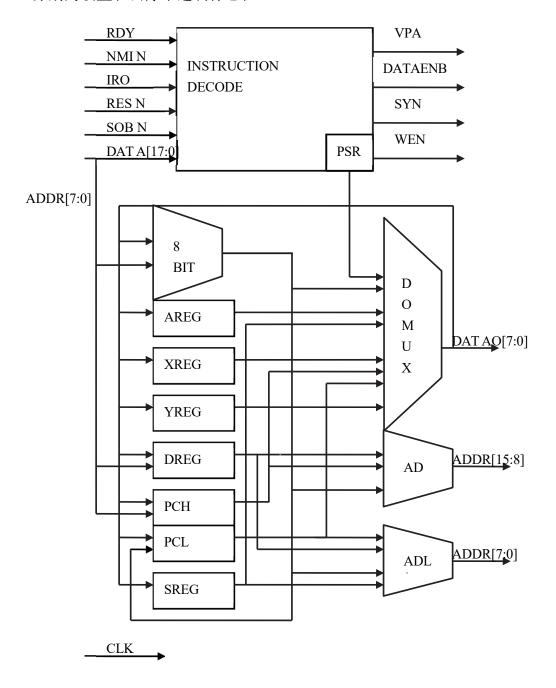

M6502 采用 CISC 结构,指令为多周期执行,在指令执行的最后一个周期根据 PC 指针从 ROM 中预取指令,然后进行指令译码,译码后,处理器将从存储器或数据总线上读取数据存入到寄存器或 ALU 中,进入到执行状态,ALU 完成运算后将运算结果通过回写模块写回到寄存器或存储器中[18]。图 2-1 为 M6502 体系结构框图。

其中,指令译码器 (INSTRUCTION) 对 M6502 指令执行的整个过程进行控制; 算术逻辑单元 (ALU) 具有以下三个方面的功能: 算术逻辑运算,地址计算,数据直通/暂存; 寄存器 A 为累加器,一般情况下用于存储源操作数和目标操作数; 寄存器 X、Y 为索引寄存器,指令采用索引寻址方式时,由 X、Y 提供索引地址; 寄存器 D 为处理器 的数据缓存器,用于存储临时数据; 寄存器 PSR 为状态寄存器; 16 位程序计数器 (PC) 为处理器提供取指地址; 堆栈指示器 (S) 为处理器提供堆栈指针; 数据输出多路选择器 (DOMUX) 对 寄存器数据或 ALU 计算结果进行选择输出,为 M6502 的数据输出; ADH、ADL 分别选择输出地址高 8 位和低 8 位,为 M6502 的地址输出[1920]。

#### 2.2 M6502 指令集

M6502 共有 69 条指令,结合 15 种寻址方式,产生 210 种操作码,指令长度最长为 3 个字节,最短为 1 个字节。指令执行周期最长为 7 个时钟周期,最短为 2 个时钟周期。

以下根据指令功能将 M6502 指令分为 13 类进行描述:

- (1) 寄存器载入和取出指令,包括: LDA、LDX、LDY、STA、STX、STY,前 3条指令更能分别为将存储器的数据装载到寄存器 A、X、Y,后3条指令功能为将寄存器 A、X、Y存储的数据装载到存储器内,这类指令的操作不影响状态寄存器。

- (2) 算术运算指令,包括:ADC、SBC。ADC为进位加法指令,功能为将累加器 A 内数据与操作数和进位标志位相加,结果存回至 A 以及状态寄存器中,ADC 指令对状态寄存器的影响:当二进制加法之和大于十六进制数 FF 或十进制。SBC为借位减法指令,执行 SBC指令时,必须将状态寄存器的进位标志位设置为 1,指令执行时,将累加器 A 数据与操作数相减,

并减去进位标志位的补码,将运算结果存回累加器 A。M6502 可以进行二进制和十进制运算,由状态寄存器的十进制运算标志位控制,SED、CLD 指令分别为设置和去除十进制标志位<sup>[21]</sup>。

图 2-1 M6502 体系结构图

(3) 加一减一指令,包括: INC、INX、INY、DEC、DEX、DEY。INC

指令功能为将存储器数据加 1 并存回原来位置,INX、INY 指令功能分别 为将索引寄存器 X、Y 数据加一存回寄存器 X、Y。DEC 指令功能为将存储器数据减 1 并存回原来位置,INX、INY 指令功能分别为将索引寄存器 X、Y 数据减一存回寄存器 X、Y。

- (4) 存储器数据计算指令,包括: RMB、 SMB、 TRB、 TSB, 其中 RMB、SMB 指令的功能分别为对零页数据某位写 0 或写 1, TRB、 TSB 指令分别将存储器数据与累加器 A 数据做与非、或运算,然后写回到原来存储位置。

- (5) 逻辑运算指令,包括: AND、ORA、EOR, M6502 可进行三种逻辑运算,分别为与、或、异或。执行以上三条指令时,处理器分别将操作数与累加器 A 做与、或、异或运算。AND 指令主要用于屏蔽累加器 A 的某个位元,再使其进行某种运算。ORA 指令最主要的用途是将累加器 A 的某个位元设置为 1。EOR 指令既可以用于判断两个操作数,有哪几个位元不同,也可以用于将累加器 A 的某些位元取补码。

- (6) 寄存器传输指令,包括: TAX、TAY、TXA、TYA、TSX、TXS, 这类指令功能是完成数据在处理器 及存器间的数据传输。

- (7) 比较与位检测指令,包括: CMP、CPX、CPY、BIT, 前三条指令的功能分别是将累加器 A、索引寄存器 X、Y 数据与操作数进行比较,这三条指令不改变操作数或寄存器内的数据,只改变状态寄存器的标志位。执行 CMP、CPX、CPY 指令时,处理器将寄存器数据减去操作数,但不存储计算结果,只更新负值标志位(N)、零值标志位(Z)和进位标志位(C),通过这三个标志位就可以判断比较结果。

- (8) 移位与旋转指令,包括: ASL、LSR、ROL、ROR,ASL 指令的功能是将操作数左移一位,并将原最高位赋值给进位标志位,同时将最低位补充为 0,LSR 指令的功能是将错作数右移一位,最高位补充为零,最低位作为进位,ROL 指令可以将错作数向左旋转一位,最高位作为进位标志位(C),然后将 C 赋值给操作数最低位。

- (9) 跳转和分支指令,包括: JMP、BBR、BBS、BCC、BCS、BEQ、BNI、BNE、BPL、BVC、BVS、BRA,JMP为无条件跳转指令,程序遇到此指令的时候发生跳转,采用绝对寻址或间接绝对寻址两种寻址方式,JMP指令执行时,处理器将程序计数器数据加操作数,得到新程序指针,处理器执行的下一条指令将从新 PC 指针位置读取。分支指令也可以成为条件跳转指令,只采用相对寻址方式,BBR、BBS 指令通过判断存储器数据进行跳转,指令长度为 3 个字节,第一个字节为操作码,第二个字节为跳转条件,第三个字节为跳转步长,其他 9 条分支指令通过判断状态标志位进行跳转,指令长度为 2 字节,第一个字节为操作码,第二个字节为跳转步长[22]。

- (10) 堆栈指令,包括:PHA、PHP、PHX、PHY、PLA、PLP、PLX、

PLY, 堆栈指令分为入栈和出栈两类, 前 4条指令为入栈指令, 分别将寄存器 A、PSR、X、Y的数据压入堆栈, 后 4条指令为出栈指令, 分别从堆栈中取出寄存器 A、PSR、X、Y的数据, 此类指令都采用隐含寻址的方式指令执行需要 4 个周期。

- (11)状态标志位设置指令,包括: CLC 、 CLD 、 CLI 、 CLV 、 SEC 、SED、SEI,前四条指令的功能分别是将进位标志位 C、十进制运算标志位 D、中断请求禁能信号 I、溢出标志位 V 清零,后三条指令分别将 C、D、I 设置为 1。

- (12) 子程序跳转和中断指令,包括: JSR、RTI、RTS、BRK,当由于某种原因处理器需要执行自程序时,就会用到 JSR 指令,JSR 指令只采用绝对寻址方式,指令长度为 3 字节,第一个字节为操作码,第二和第三个字节为新的 PC 指针数据,执行 JSR 指令时,处理器首先读取操作码,再读取第二和第三个字节的跳转数据,即操作数,并存储于数据寄存其中,之后的两个时钟,处理器分别将 PC 寄存器的低位和高位压入堆栈,然后再将跳转数据赋予 PC,下条指令将从新的 PC 指针指向的程序存储器地址读取,自程序执行完后,处理其需要继续原来工作,就执行 RTS 指令,将压入堆栈中的 PC 数据读回并赋予 PC,完成程序的返回。当处理器决定进行中断处理时,采用隐含寻址方式,指令长度 1 字节指令执行 7 个周期,执行 BRK指令时,处理器第一个周期将中断标志为 B 设置为 1,之后的三个时钟周期分别将寄存器 PC、PSR 数据压入堆栈,然后读取中断向量低位,并赋予 PCL同时将中断请求禁能信号 I 设置为 1,第六个周期读取中断向量高位,并赋予 PCH,第七个时钟用于更新寄存器 PC,中断处理完成后使用 RTI 指令将存入堆栈 PC、PSR 数据取出,继续原来的程序执行[23]。

- (13) 无运算指令: NOP, 这条指令不会影响任何寄存器或存储器的数据, 主要用于两方面, 即可以为程序设计者保留存储器空间以便以后在该位置添加指令, 也可以用于填补被程序设计者去除的指令的位置。

## 2.3 M6502 寻址方式

M6502 可以采用 15 种寻址方式进行工作,以下分别对这 15 种寻址方式进行了详细的介绍,包括指令采用此种寻址方式时的执行情况说明。

立即寻址(IMM):采用立即寻址方式的指令长度为 2 字节,第一个字节为操作码,第二个字节即为操作数。指令执行时,处理器首先读取操作码,然后就读取操作数进行运算。

绝对寻址(ABS):采用决对寻址方式的指令长度为 3 字节,第一个字节为操作码,第二和第三个字节分别为操作数的低位地址和高位地址。零页寻址(ZPG):零页寻址其实是绝对寻址的一种,不同的是,在零页寻址方式中,操作数仅处于 ROM 的前 256 个存储地址,即分页结构中的零页,此位置的十六进制数为 0000 到 00FF,由于高位地址为 00,因此在零页寻址时给

以上内容仅为本文档的试下载部分,为可阅读页数的一半内容。如要下载或阅读全文,请访问: <a href="https://d.book118.com/71702613510">https://d.book118.com/71702613510</a>

4006141